生物电阻抗测量系统中弱信号检测技术研究--弱信号检测调理单元设计与实现

4.2.2.1射随电路设计分析

射随电路主要功能是保持输入信号的幅频特性,即保持信号幅度和频率不变。但是在射随前端须保证信号的完整性且信号具有较小的衰减,在射随的输出端与输入端保持幅度和频率的一致并且具有较强的驱动能力,因此射随电路必须具有较高的输入阻抗和较小的输出阻抗。射随电路的设计,是基于以下考虑设计的:

1.完成射随功能。使输入信号通过电路保持信号完整性。

2.确保性能指标完全实现。系统设计的根本依据是系统所要达到的性能指标,因此系统性能指标需首先得到保证。如输入阻抗大于1M等。

3.模块设计的灵活性。电源激励信号非常微弱,而且动态范围较大。场效应放大电路模块设计需具有适应动态范围大的特点。

4.安全可靠性。有足够的抗干扰能力,要保证在规定的工作环境下,系统能稳定,可靠地工作。保证系统精度能符合要求。

5.信号频率考虑。射随电路的频带必须大于250MHz. 6.经济性原则。在遵循以上设计原则的条件下,在器件选择上尽量以完成相同的功能的基础上选择那些价格相对来说比较低一些的器件为标准,这样可以有效地降低生产成本,为产品进入市场打下良好的基础。

4.2.2.2 ADA4817芯片的应用

ADA4817是一款稳定的单位增益放大器,它提供超高速电压反馈,场效应输入。该放大器能获得超低噪声和高输入阻抗。ADA4817输出0.1Vpp时,信号有效带宽1050MHz,满足频带要求。

ADA4817从模拟设备上引出一条新的低失真引出线,相比于传统的引出线,该低失真引出线有两个优势。一是能改善二次谐波失真性能,它能物理隔离放大器的输入管脚和负电接入管脚电路。二是布局简单,它能提高倒相输入,允许紧密的布局和轻易的布局,帮助减小寄生增益和稳定性增长。

宽泛的带宽和较低的噪声使之成为放大器的理想选择,特别是在高速采集信号检测预处理的应用。

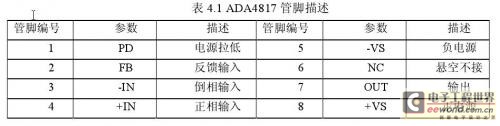

ADA4817各管脚描述如表4.1所示:

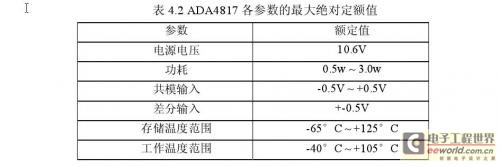

ADA4817各参数的最大绝对定额值如表4.2所示:

4.2.2.3射随放大电路设计

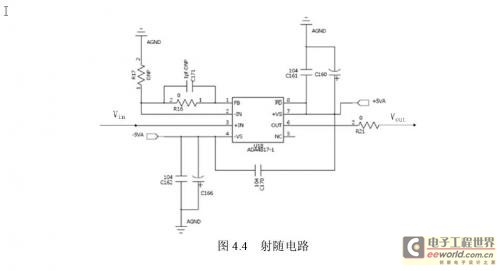

场效应放大器广泛用于数据采集系统,射随电路采用ADA4817芯片。本文设计该电路主要完成射随电路功能。

射随电路设计方案如图4.4所示。

4.2.3可编程增益放大电路

模块高速数据采集的前端信号,是频率和电压不确定的模拟信号。因为固定增益将使得大信号进入非线性工作区且可能导致放大信号超出数据采集的量程范围而出现信号被削平的现象,或者使得小信号放大不足,不能使放大信号达到或接近数据采集的量程范围而产生较大的量化误差。同时在仪器仪表中所要测量的信号其动态范围往往很宽,如在测量峰形信号的系统中,可能既有峰值很小的峰信号,又有峰值很大的峰信号。若放大通道不能随输入信号动态范围变化,而做出相应的增益调整,将会降低整个系统的分辨率及性能。由上述可知,放大通道必须增益程控可调,不能够采用固定增益的放大电路。

4.2.3.1 PGA870的应用

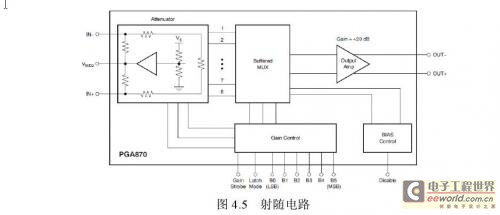

PGA870是一款高速全差分可编程增益放大器。它的高带宽、低失真、低噪音特性使它非常适合与14位ADC配合使用,其增益调节范围为-11.5 dB到20dB,增益步幅为0.5dB,增益准确度为0.03dB.频带范围为650MHZ.其内部结构图如图4.5所示。

从图中可以看出,输入差分信号依次经过衰减器、放大器、输出控制器,衰减倍数和放大倍数由控制逻辑位B0-B5和gain strobe、latch mode管脚控制。在power-down状态,静态电流降至2mA,但是增益控制电路仍能保持可编程。

4.2.3.2可编程增益放大电路的设计

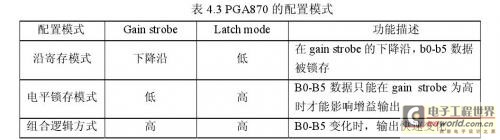

为实现信号增益可控,设计中选择PGA870芯片,因为PGA870有三种配置模式,分别是电平锁存模式,沿寄存模式,组合逻辑方式,由配置管脚gain strobe和latch mode控制,其配置方式如表4.3所示。

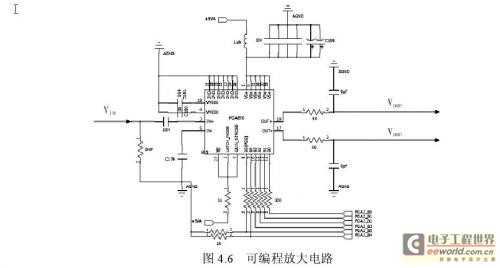

组合逻辑方式的信号延迟最小,实时行相应最好,且配置方式需要的线也最小,只需将B0-B5连接到FPGA管脚上,Gain strobe和Latch mode接到3.3V上就可以了,综上,PGA870的配置方式采用组合逻辑方式,其在电路中的设计图如图4.6所示。

图中,为了减小信号反射的幅度,在B0-B5上均串联上一个电阻。为了减小前端直流偏置对本模块的影响,同时考虑到芯片内部已经提供了一个内部参考电压,信号输入端采用交流耦合方式,耦合电容选用较大值0.1uf,以让低频信号无衰减通过。因为放大器的输出电阻只有3.5欧姆,为实现信号的50欧姆端接,输出串联50欧姆电阻。

4.2.3.3可编程增益实现方式

可编程增益放大的实现由FPGA来完成,如图4.7所示,FPGA通过逻辑控制来确定配置模式,通过控制放大器的B0至B5管脚控制运放的增益。

评论