开放式FPGA可增加测试的灵活性

闭环测试:功放

在无线通信系统中,信号在发往天线之前需要用功放IC增加信号的强度。功放的性能规格通常是在特定的输出功率电平点定义的。因此当功放工作在这个输出功率电平时对它们进行测试就显得非常重要。然而,功放的增益一般只是粗略的知道(比如±3dB),而且在器件工作范围内是非线性的。你越接近最大输出功率,增益就越低。基于这些理由,在开展任何性能测试之间你必须首先“调测”放大器的输出。调测输出经常被称为功率电平调整或功率伺服调整。基本原理是调整放大器的输入功率,直到你测得正确的输出功率。

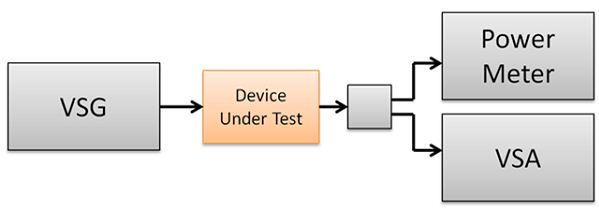

测量功放的传统测试装置见图3所示。矢量信号发生器(VSG)产生一个激励波形给待测设备。功率计确保待测设备输出正确的功率电平。最后由矢量信号分析义(VSA)测量待测设备的性能——如误差矢量幅度(EVM)或相邻通道功率(ACP)。实际操作中需要针对各种中心频率和功率电平重复这些测量。

图3:用于测量功放输出的传统测试装置包含有矢量信号发生器、矢量信号分析仪和功率计。

必须针对每个想要测试的中心频率和功率电平调测功放的输出功率。调测过程一般遵循以下这些步骤:

● 根据估计的待测设备增益选取一个起始的矢量信号发生器功率电平

● 设置矢量信号发生器的功率电平

● 等待矢量信号发生器稳定工作

● 等待待测设备稳定工作

● 用功率计进行测量

如果功率在正确的范围内,退出。如果不在范围内,计算新的矢量信号发生器功率电平,回到步骤2重新开始

整个调测过程可能要花几百毫秒到几秒的时间,具体取决于待测设备类型、要求的精度以及使用的仪器。调测过程完成后就可以用矢量信号分析仪开展性能测量了。

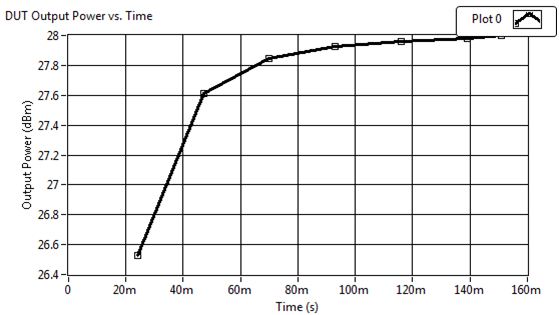

图4显示了使用传统方法将待测设备样品输出调整到平均输出功率为28dBm的过程。如果功率放大器的增益是线性的,并且符合数据手册中规定的典型增益,那么矢量信号发生器产生的第一个点就将产生28dBm的输出功率。然而放大器的实测输出功率只有26.5dBm,这就表明了功放典型增益指标的不精确性。随后调整矢量信号发生器的输出功率,由矢量信号分析仪捕获另外一个输出功率点。这次平均功率是27.6dBm,从中可以看出放大器增益响应的压缩过程。总之花了7步、大约150ms的时间才使放大器的输出达到想要的功率值。在这个例子中,待测设备的稳定时间是每步10ms。但不同待测设备的稳定时间是不同的,它将显著影响总的调测时间。

图4:传统的功放输出调测方法表明功率电平是渐次增加的。

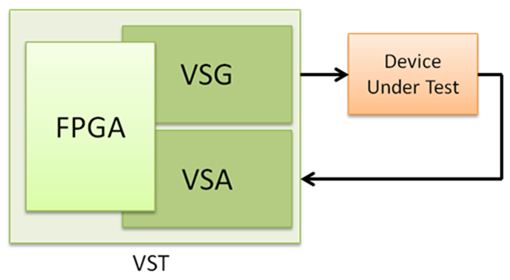

矢量信号收发器(VST)是将矢量信号发生器、矢量信号分析仪和FPGA整合在一起的一种仪器。这种组合可以让你将功率调测算法转移到硬件中实现。即使没有图5中的功率计,你通常也可以执行系统校准步骤将功率计精度转嫁给矢量信号分析仪。

图5:矢量信号收发器将信号发生器、信号分析仪和FPGA整合在一起。

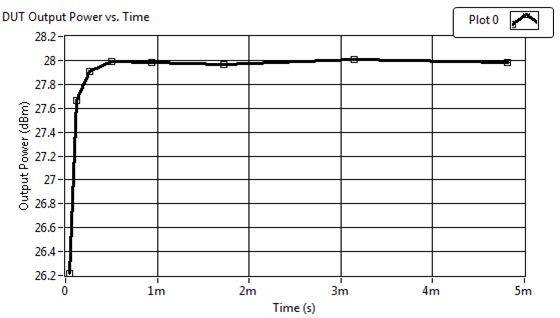

调测功放输出功率的步骤与传统方法是类似的,只不过调测环路在开放式FPGA中执行。在FPGA中执行环路可以显著缩短每次调整所需的时间。

通过使用开放式FPGA和硬件并在FPGA上实现控制环路,调测待测设备输出功率的时间将远远小于在主机电脑上执行控制环路的时间。对于本例中的待测设备来说,调测过程只用了5ms,而传统方法需要150ms。需要注意的是,基于硬件的方法所需的步骤数比传统方法多一步。但调测过程所需的总时间却明显减少。与图4相比,图6中的前几个步骤完成得很快(平均时间较短),然后点的间隔越来越大,因为调测环路正在收敛。

图6:使用基于硬件的调测方法后,功率电平上升的时间要短于传统方法。

信号处理

用户可编程FPGA最有用的应用之一是在仪器上减少必须传回主机进行后处理的数据量,从而释放通信总线用于其它数据传输,同时减少CPU的负担。用于这方面的常见方法包括复杂触发、滤波、峰值检测或对捕获的数据集执行快速傅里叶变换(FFT)。

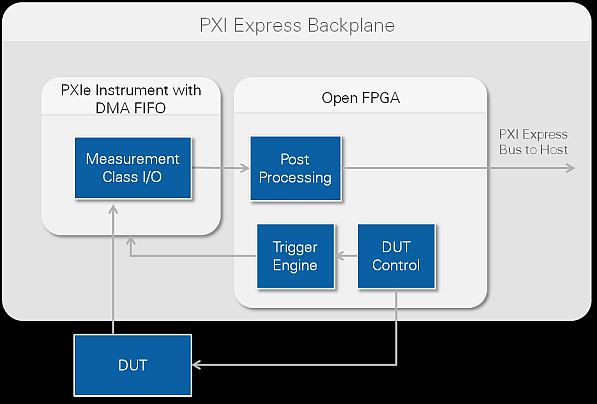

例如在图7中你可以看到有4个待测设备需要并行测试的应用。模数转换器(ADC)将样本传送给FPGA,但直到定制触发器启动捕获命令后数据才被捕获。在捕获数据时,FPGA会实时平均测量结果,然后将它们连续进行记录。然后在测量无杂散动态范围(SFDR)、信噪比(SNR)和信号噪声与失真比(SINAD)之前对记录进行快速傅里叶变换。这些结果只是来自ADC的的输入信号数据的一部分,接下来将通过直接存储器访问先入先出缓冲机制(DMA FIFO)上传给主机。

评论