开放式FPGA可增加测试的灵活性

目前大多数仪器采用封闭式FPGA(现场可编程门阵列)和固定的固件实现仪器的功能。如果你曾见过示波器的拆解,你也许见过里面的FPGA。FPGA可以增加测试仪器的处理能力,如果你曾使用过仪器的开放式FPGA,你就会知道可以将自定义的测试功能编程进仪器中。

仪器供应商早就了解FPGA的好处,并且一直在充分发挥FPGA独特的处理能力优势来丰富的功能,比如:仪器

● 能够在示波器上完成预触发捕获

● 能够利用信号处理功能在矢量信号分析仪上产生I和Q数据

● 能够在高速数字仪器上实时进行图案发生和矢量比较

测试设备制造商现在开始向用户开放FPGA以提供更多特殊应用的优化。为了帮助理解为何这是一个好的转变,下面列出了在测试应用中使用FPGA的一些关键特性:

● 确定性,实时处理

● 真正并行的执行

● 可重配置

● 低延时

更进一步讲,利用开放式FPGA可以实现哪些以前不能实现的功能呢?为了描述这些可能性,下面将介绍一些利用开放式FPGA的常见测试应用。

测试系统加速

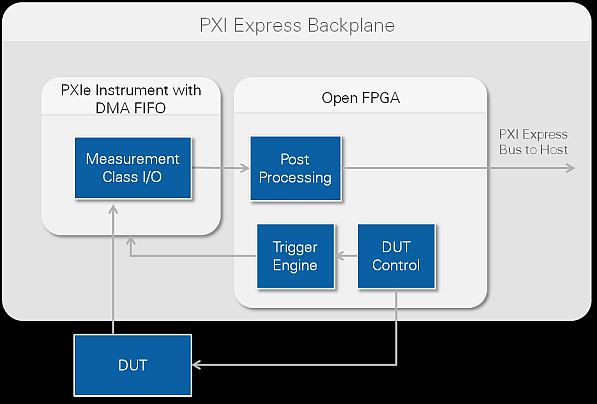

在大批量生产线的最终产品测试中,每一秒的测试时间都很宝贵。当产品测试速度与生产速度相匹配时,生产线的效率就是最高的。当两者速度不匹配时,就必须采用创新的技术来缩短测试时间。传统方法需要使用多台分开的台式仪器,它们通过以太网、USB或GPIB连接到一台PC主机。这种测试的速度相对较慢,因为待测设备的控制、测量以及通过数据总线的处理是分开进行的。另外一种方法是使用开放式FPGA来加速这个过程,如图1所示。

图1:在测试仪器中,开放式FPGA可以增加诸如触发和后处理等功能。

与使用外部通信总线不同,FPGA可以使用高速总线(如PXIe)连接仪器,并通过其配置端口(如I2C、SPI或另外的控制总线)连接待测设备(DUT)。这种应用中的FPGA可以控制待测设备,触发其它仪器开始捕获样本,甚至将这些样本处理成对主机来说有意义的结果。

低时延是加速这类应用的一个关键因素。FPGA没有操作系统,但所有的逻辑都是用硬件实现,并且这些硬件工作的时钟速率很高。这意味着响应只需花一个时钟周期捕获、一个时钟周期处理和一个时钟周期输出结果。当时钟速率为200MHz(时钟周期为4ns)时,完整的响应时间只需12ns。由于FPGA的确定性特点,12ns的响应时间不是只有一次,而是每次都是。因此FPGA不仅可以避免与使用主机有关的延时,而且能够最大限度地减小主机处理时的非确定性延时。

协议的处理

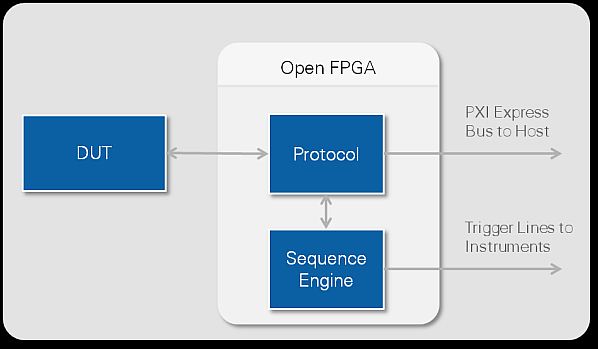

今天,并不是所有数字和MEMS设备都能用已知结果矢量进行测试。就拿脉冲密度麦克风(PDM)来说,如果给它一个激励信号,你不能期望每次测试得到的比特流是完全相同的,这是因为PDM是模拟设备。为了从这些类型的待测设备获得有意义的结果,在比较结果之前你首先需要用其特定的协议对数字流进行解码。借助开放式FPGA,你可以在FPGA上配置你的测试系统来实现PDM协议,不必再传至CPU进行解释。进一步拓展这个概念,今天你可以配置这个FPGA实现PDM协议,明天你又可以重新配置同样这个FPGA实现不同的协议,比如用于测试数字温度传感器、加速度计或MEMS设备的协议。

在图2中,协议不是在CPU上实现,而是在FPGA上实现。正因为此,测试系统现在自身就可以支持快速握手脚本,适应精确等待周期等协议行为,并根据通信内容做出决策。这种方法不仅能让你从待测设备接收更高层数据,比如在PDM麦克风场合中解码的模拟数据,而且允许你用更高层命令编写测试脚本。

图2:FPGA可以用来处理协议,知晓总线使用的协议内容。

评论