前言鉴于鉴定当前射频微波器件和系统行为特点的挑战,必需了解频率、幅度和调制参数在短期和长期内的行为方式。在这些情况下,使用传统工具如扫频分析仪(SA)和矢量信号分析仪(VSA)可能会在频域和调制域内提供信号概况,但其通常不能提供足够的信息,让工程师满怀信心地描述器件或系统生成的动态射频微波信号。

考虑一下下面挑战性的测量任务:

本文引用地址:https://www.eepw.com.cn/article/201701/337203.htm- 发现罕见的短时间周期事件

- 查看较强的信号掩盖的较弱信号

- 观察噪声掩盖的信号

- 查找和分析瞬态信号和动态信号

- 捕获突发传输、毛刺、开关瞬态事件

- 检定PLL 稳定时间、频率漂移、微音扩大

- 捕获扩频信号和跳频信号

- 监测频谱使用情况,检测游荡传输

- 测试和诊断瞬态EMI 效应

- 检定随时间变化的调制方案

- 隔离软件和硬件交互

每种测量都涉及随时间变化的射频微波信号,这些信号通常是不可预测的。为有效检定这些信号的特点,工程师需要一种工具,这种工具要能够发现难检事件,有效触发这些事件,把事件隔离到存储器中,以便能够在频域、时域、调制域、统计域和码域中分析信号行为。

实时频谱分析仪硬件架构

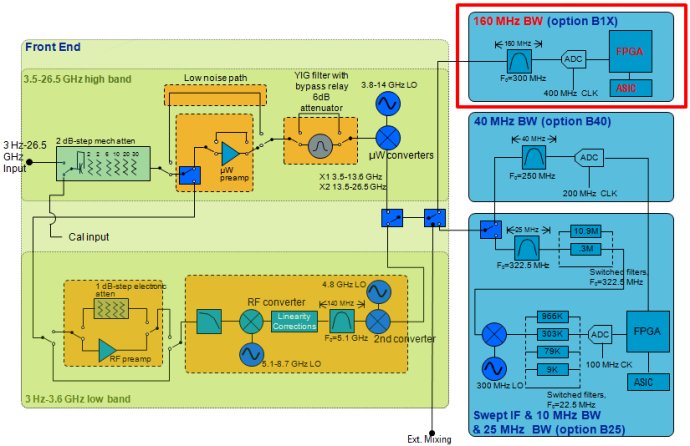

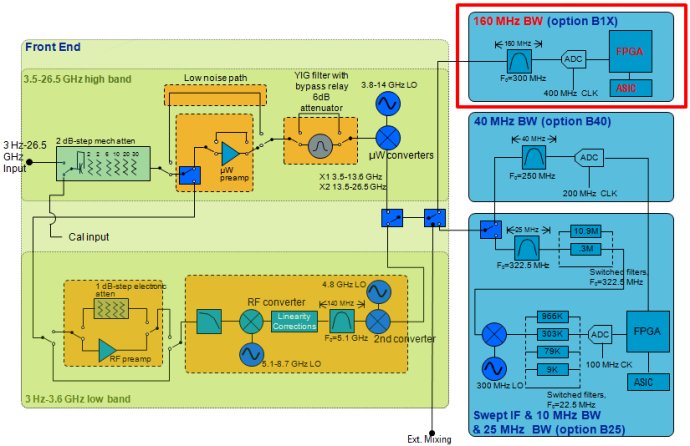

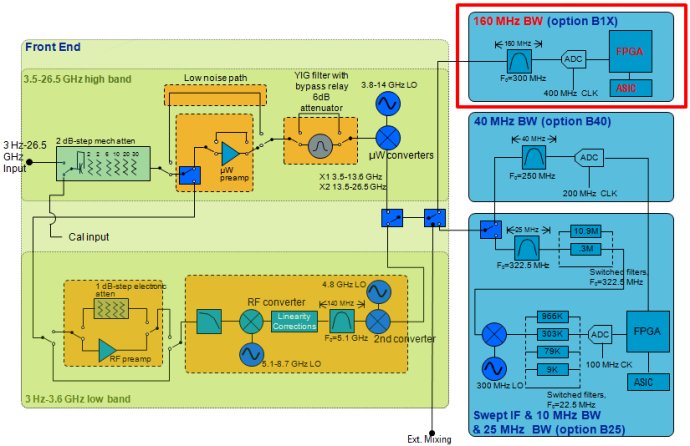

安捷伦实时频谱分析仪是在PXA的B1X选件基础上,用Xilinx的FPGA做实时信号处理所产生的新产品。如图1所示,图中是一个26.5GHz的PXA频谱分析仪,模拟变频部分与传统频谱分析仪一致,只是在B1X选件即160MHz分析带宽选件里,用一块包括实时处理引擎的FPGA做实时信号处理,形成实时频谱分析仪。这个FPGA所做的事情,其结构框图如图2所示。

图1PXA频谱分析仪结构框图

图2FPGA实时处理引擎结构框图

FPGA内的实时处理引擎功能框图如图2所示。14位、400MHz的ADC采集的中频数据输入到FPGA,FPGA各种内核关键处理的内容如下:

1.幅度和相位校正,下变频和压缩处理

幅度和相位校正用于校正信号路径的幅度平坦度和相位线性度及其它不理想内容。

下变频是把采集的中频信号用数字信号处理DSP下变频的方式转化为I和Q基带成分。ADC在高中频IF上进行模拟到数字转换而不是在DC或基带上进行模拟到数字转换,具有信号处理的优势,如提升杂散性能、DC抑制、动态范围等。下变频是通用的DDC原理,包含一个数字振荡器,其在关心的中心频段上生成数字正弦和数字余弦信号。数字正弦和数字余弦信号乘以数字IF,生成I和Q基带数字信号。DDC不仅用来把数字IF信号转换成基带信号,还用来进行实时频谱分析仪中的频率微调。

压缩处理是通过降低采样率,平衡频宽、处理时间、记录长度和存储器使用量。奈奎斯特定理指出,对于基带信号,只需以等于关心的最高频率两倍的速率采样即可恢复信号;对于通带信号,采样率至少是带宽的两倍。400MHz的ADC数字化信号通过DDC后,对于160MHz带宽,I和Q采样率只要一半即200MSa/s。样点总数未变,但得到了两个样点集,每个样点集的有效采样率是200MSa/s,而不是速率为400MSa/s的单集。对于更窄的频宽,将进行进一步压缩,使得对相同数量的样点得到更长的时间记录长度。压缩的缺点是降低了时间分辨率,优点是在时间记录长度一定时减少了计算工作,降低了存储器的使用量。

在压缩时也必须遵守奈奎斯特定理,如果数据速率下降两倍,那么数字信号的带宽也必须下降两倍。在降低采样率前,需要使用数字滤波器完成这一点,以防止出现假信号。压缩和滤波的另一个优势是在带宽下降时降低噪声。

2.实时处理和重叠存储(Overlap Memory)

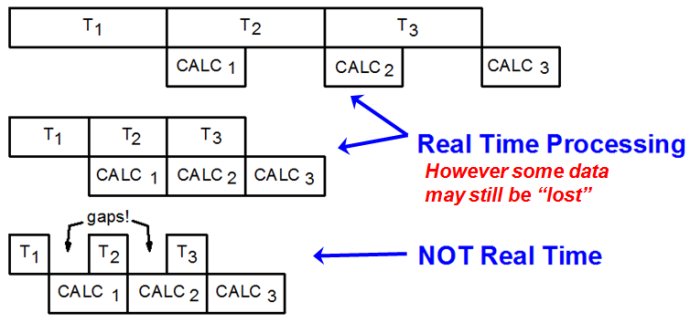

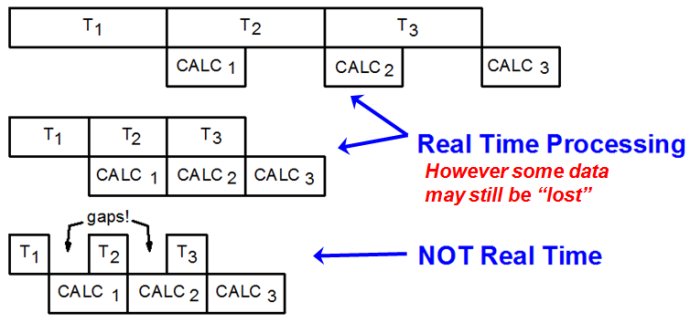

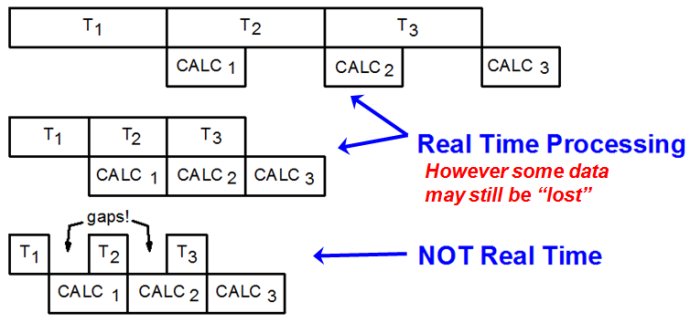

先看一下实时处理的概念,如图3所示。T是存储器里存储的数据,CALC是每帧数据处理的时间。CALC时间包括FFT或功率谱,平均处理,显示刷新时间等。如果CALC时间大于每帧的时间,则是非实时处理,传统的频谱分析仪即是非实时处理。CALC时间等于或小于每帧时间,则是实时处理。如果仅仅是等于每帧时间,也可能会丢掉一些数据,所以需要小于每帧的时间。

图3实时处理的概念

因为进行FFT运算时需要加窗函数,这时如果要避免由于窗口导致的数据丢失,和要保持幅度精度,需要重叠存储,如图4所示。比较理想的状况是重叠50%,这需要CALC的时间等于或小于每处理帧时间的50%。

评论