基于CPLD/FPGA/MCU的CAN-VME总线转换方案

本文提出了基于FPGA的VME总线和CAN总线之间的传输转换方案,满足一些特殊工业环境的需要,具有一定的研究意义和实用价值。

1 转换系统的硬件设计

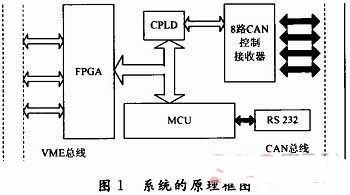

该系统由VME总线接口模块、CAN总线节点(8路CAN节点)模块、复杂可编程逻辑器模块、MCU模块4部分核心模块构成。整个系统在一个3U标准的VME板卡上实现,机构紧凑,布局合理。系统的原理框图如图1所示。

1.1 VME总线接口模块

整个系统实现是两种通信之间的转换,所以数据的发送都是由上位主机发送的。由于FPGA控制灵活,所以很方便实现与VME总线的连接。文中FPGA器件选用XILINX公司的XC2S200系列的5PQ208,56 Kb专用存储器,最高运行速度200 MHz,I/O电压在3.3~5.5 V,地址总线、数据总线,/AS,/IACKIN,/IACKOUT,SYS CLK等可以直接与5PQ208连接。

1.2 CAN总线节点模块

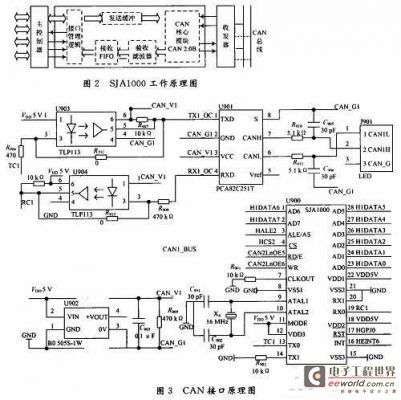

CAN总线节点模块是该系统中的主要模块,选用Philips公司生产的SJA1000,它负责连接总线与8路CAN选通主控制器CPLD之间的数据通信,其整个系统功能如图2所示。收发器选用P82C251T。CAN接口原理如图3所示。

1.3 复杂可编程逻辑器件(CPLD)模块

在系统中,由于FPGA的地址总线和数据总线是分开的,而SJA1000的地址和数据线是分时复用的,所以在总线接口上有一定差异,因此选用MAX3000系列可编程逻辑器件EPM3128来进行逻辑变换。该CPLD芯片有丰富的宏单元,80个用户I/O管脚,管脚间延迟时间是10 ns,最高速度可达100 MHz,能够满足系统设计的需要。可编程逻辑器件在系统中的功能为:转换FPGA与CAN控制器SJA1000之间的地址总线和数据总线;通过对FPGA的地址线译码,扩展CAN控制节点的通道。

1.4 MCU处理器

由于CAN总线的最高传输速度是1 Mb/s,所以该部分选取宏晶STC12C5A60S2,FLASH程序存储器为56 KB。SRAM为1 280 B,2个专用的UATR,丰富的CPU资源满足作为下位机的CPU控制单元,主要完成两种总线协议的转换,负责将从FPGA过来的VME总线转换成CAN总线格式,并传输到指定CAN节点;同时也将CPLD选通的CAN通道数据,转换为FPGA能识别的VME总线格式,并在MCU中断主机时,将数据反馈给VME主机。

评论