讨论s3c2440的时钟与DMA

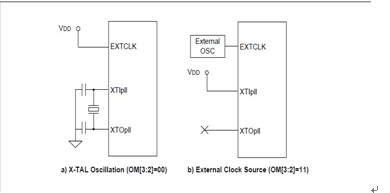

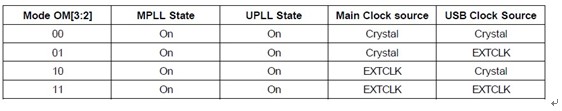

由这个表可以看出来时钟源的选择是在引导的时候由OM[3:2]引脚决定的。

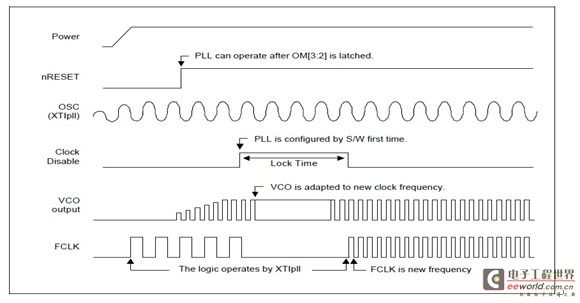

如图,刚上电一小段时间后,FCLK=晶振时钟,等待4个时钟周期后,PLL锁存有效,自动插入一段PLL Lock Time,即PLL锁定时间,此时,FCLK停止震荡,CPU停止工作,Lock time的长短由寄存器LOCKTIME设定。PLL Lock Time之后,MPLL输出正常,CPU工作在新的FCLK下。

有两个PLL,一个是MPLL,一个是UPLL。MPLL分频得到FCLK(用于CPU),HCLK(用于AHB BUS),PCLK(用于APB BUS)。UPLL产生UCLK给USB提供48M或96M时钟。上边的是s3c2440a的体系结构图,最上边的是CPU wrapper,也就是CPU核,中间的AHB BUS相当于系统总线,APB相当于IO总线。中间的Bridge相当于康柏(Compaq)公司提出的南桥。这个Bridge的作用就是连接高速和低速总线。这种结构类似于:

评论