ARM920T协处理器CP15

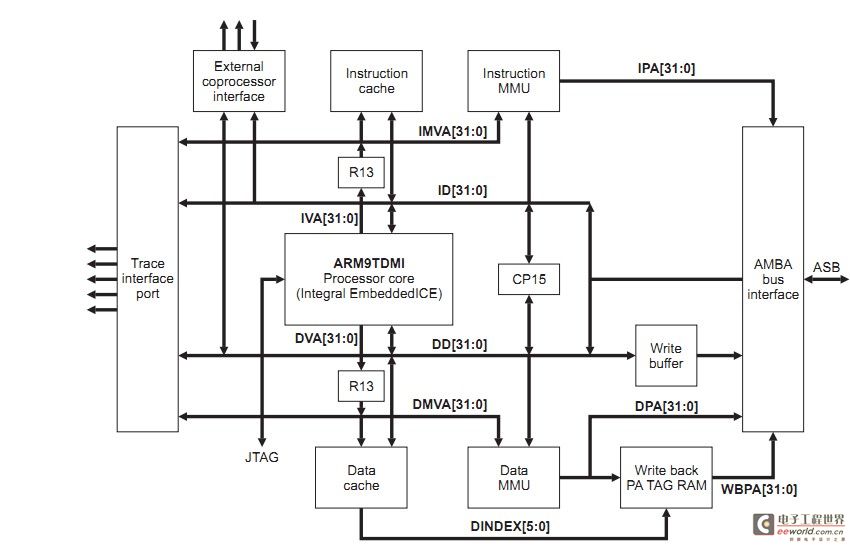

ARM920T处理器包含两个协处理器:

CP14。用于调试

CP15。系统控制协处理器,提供附加的寄存器用来配置和控制cache,MMU,保护系统,时钟模式,和ARM920T其他的系统选项,如大小端操作。你可以使用MCR,MRC访问定义在CP15中的寄存器。

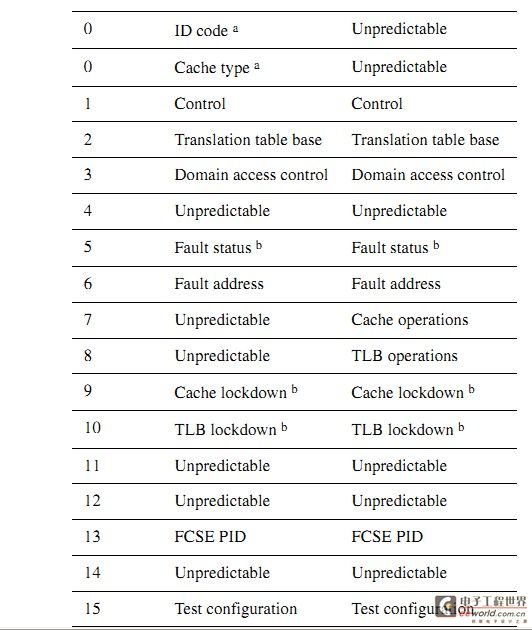

CP15定义了16个寄存器,寄存器的映射图如下:

注:寄存器位置0可以访问两个寄存器,通过opcode_2的值来确定。

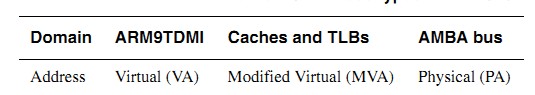

ARM920T存在3个地址。

只能在特权模式下使用MCR和MRC指令访问CP15。这些指令的格式是:

MCR/MRC{cond} P15,,Rd,CRn,CRm,

指令CDP,LDC,STC和非特权模式的MRC,MCR指令操作CP15会导致未定义指令异常。MRC和MCR指令的CRn域指定了要访问的协处理寄存器。opcode_1,和CRm域应该是0,除非值被指定用来选择需要的操作。

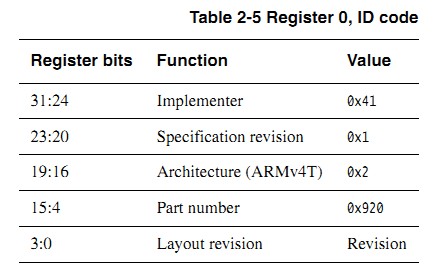

Register 0,ID code register

可以通过读CP15 register 0,opcode_2域设置成除了1的任何值(在读的时候CRm应该为0)。

如:

MRC p15,0,Rd,c0,c0,0;return ID register

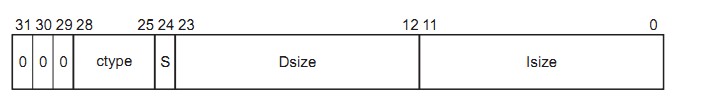

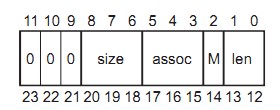

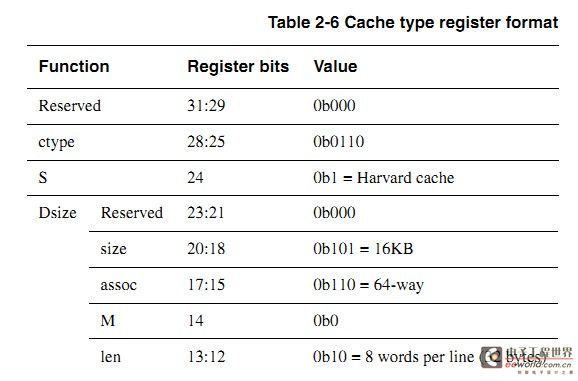

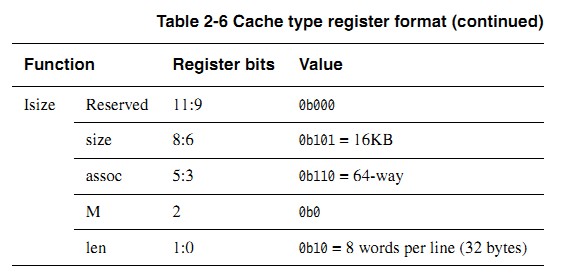

cache type register 0

包含cache的大小和体系结构的信息。可以通过设置域为1,读CP15 register 0来访问cache type register。例如:

MRC p15,0,Rd,c0,c0,1;returns cache details

Dsize和Isize域格式一样:

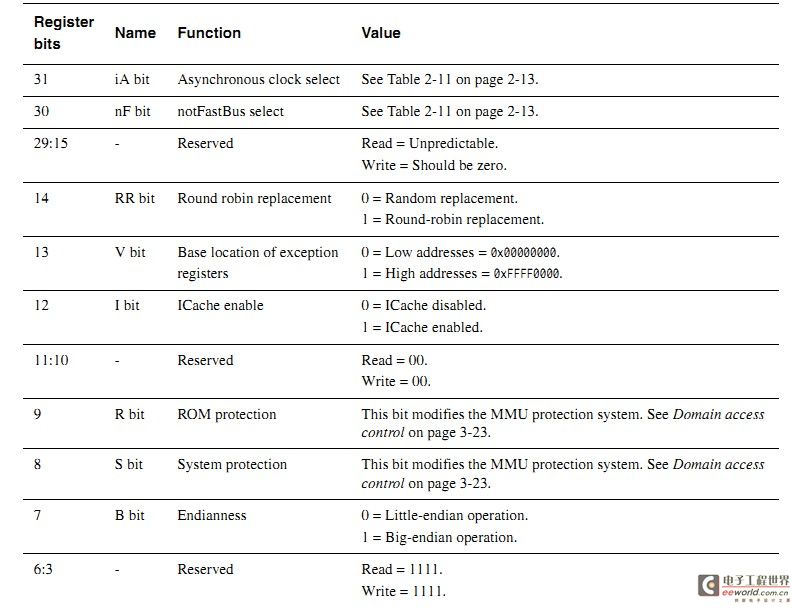

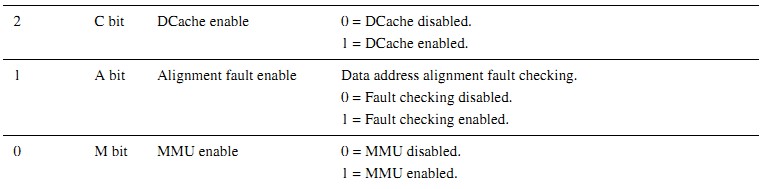

Register1,control register

这个寄存器包含了ARM920T的控制位。

MRC p15,0,Rd,c1,c0,0 ;read control register

MCR p15,0,Rd,c1,c0,0;write control register

评论