ARM920T协处理器CP15

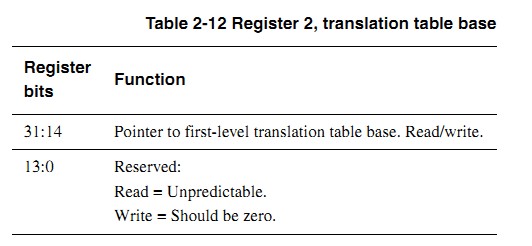

Register 2,translation table base(TTB)register

这个是页表基址寄存器。

使用下面的指令访问TTB:

MRC p15,0,Rd,c2,c0,0;read TTB register

MCR p15,0,Rd,c2,c0,0;write TTB register

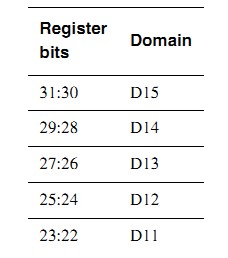

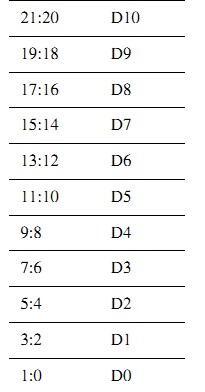

Register 3,domain access control register

这个是读写域访问控制寄存器。

MRC p15,0,Rd,c3,c0,0;read domain 15:0 access permissions

MCR p15,0,Rd,c3,c0,0;write domain 15:0 access permissions

Register 4,reserved

Register 5,fault status registers

Register 6,fault address registers

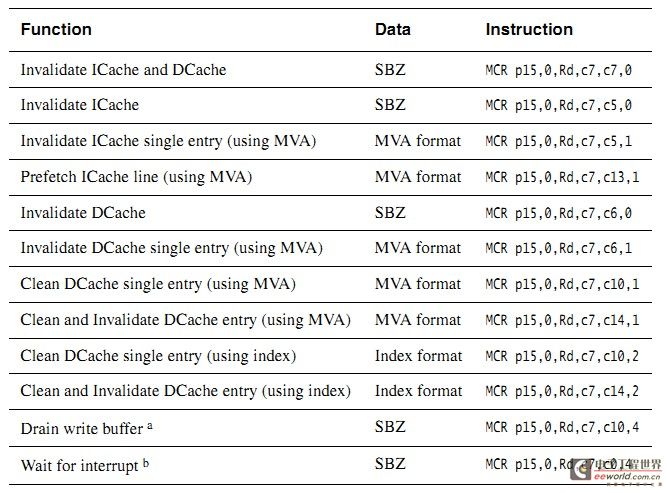

Register 7,cache operations register

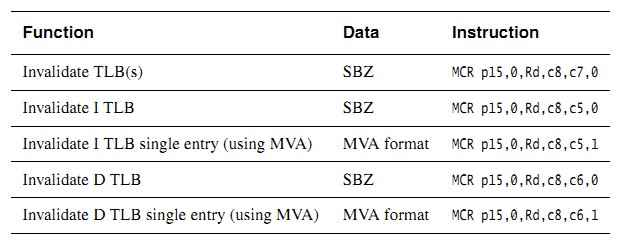

Register 8,TLB operations register

用来管理Translation Lookaside Buffers(TLBs),指令TLB和数据TLB。

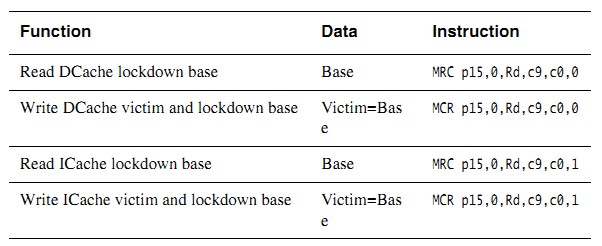

Register 9,cache lockdown register

opcode_2=0x0 访问的是Dcache

opcode_2=0x1 访问的是 Icache

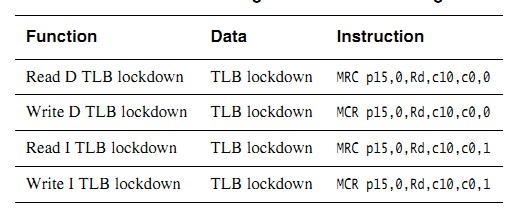

Regiter 10,TLB lockdown register

opcode_2=0x0 访问的是D TLB

opcode_2=0x1 访问的是 I TLB

Register 11,12,and 14,reserved

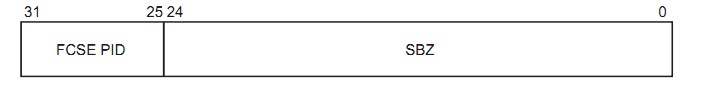

Register 13,FCSE PID register

是快速上下文切换扩展寄存器。

MRC p15,0,Rd,c13,c0,0;read FCSE_PID

MCR p15,0,Rd,c13,c0,0; write FCSE_PID

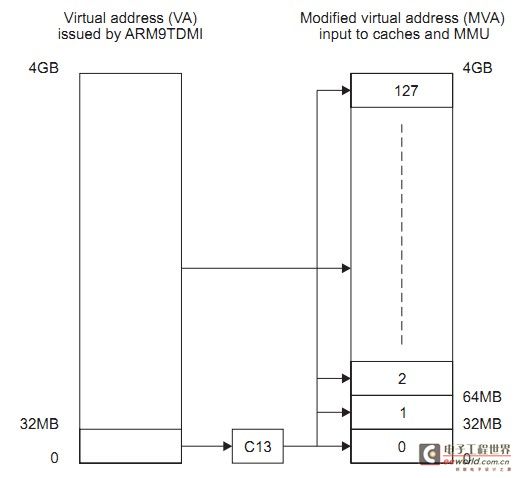

ARM9TDMI发出的地址在0~32MB范围内的被CP15的register 13转换。地址A变成A+(FCSE_PID×32MB)。FCSE_PID是一个7位的域,能够使128×32MB的进程被映射。

Register 15,test configuration register

评论