一文看懂3D晶体管

BJT晶体管通道

本文引用地址:https://www.eepw.com.cn/article/201611/339540.htmBJT的构成很简单,就是把2个P型半导体夹住1个N型半导体变成三明治。当然,也有用2个N型半导体夹住1个P型的。现在就看看NPN型的BJT如何运作。

一般而言我们把BJT的输入极称为集极,控制极称为基极,而输出极就称之为射极。由于射极要提供大量电子扩散所以杂质浓度会比较高,而基极则因为希望电流快速通过所以做得很薄。

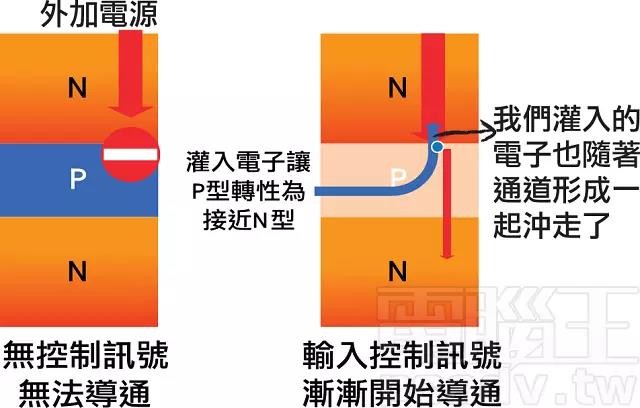

当我们由控制极输入足够的电子时,原本的P型半导体就因为充满了大量电子而慢慢把我们原本人工置入的电洞中和掉了,当然就慢慢「转性」变成N型半导体的性质。此时对于从集极加入的电压/电流来看,就会发现当P型半导体转性后,NP介面的能阶差就慢慢消失因而形成通道,而电流就会由集极一路冲向射极而发射出来,这就是通道形成的过程。

由于需要真枪实弹把电子灌进去,所以BJT的通道形成比较费力,但是通道导通的面积大所以可以流过的电流也很大,很适合高出力的工作。但是我们灌入P型半导体的电子可不会乖乖停在那里不动,它们会随着由射极出发的电子流一路冲往集极去!就像马桶把卫生纸冲掉那样(高中物理告诉我们,电流方向就是电子流方向的反方向)。

▲NPN型BJT导通情况

所以控制讯号电流不够强,是推不动BJT晶体管的。这现今芯片当中是一项很讨人厌的特性,因为它表示就算我们没什么动作,为了维持晶体管某一种状态,我们还是必需花掉大量电流!这样不但吃电很凶,还会让芯片热到可以拿来煎蛋。不过BJT的好处是整颗P型半导体都会变成通道,所以通道很宽大,推动力也就很大。

JFET

JFET 是一种类似三明治的场效应晶体管,它在接面处没有使用氧化物隔开闸极,音响迷一定不陌生, JFET的推动力大,线性高对高频反应又不良,是非常良好的音响用放大器材料。读者若想看到实体物品,走一趟发烧音响材料行一定可以看到一大堆。

MOSFET晶体管通道

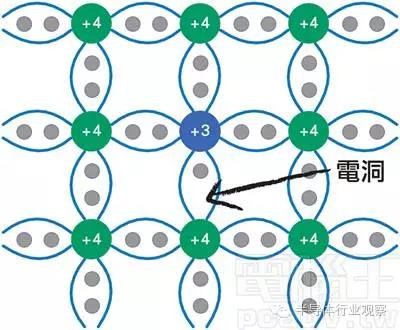

而MOS就非常小家子气了,在早期或者是大功率的JFET,是由2个N型半导体夹住P型半导体,(或者2个P型夹住N型),但是电流通过的方向和通道形成方向则和BJT呈九十度。而在半导体中的MOS就如下图所示,在FET元件当中,由闸极来的电压对晶体中间部位造成静电力,静电力则吸引了正或负电荷靠近闸极,造成晶体中央部位靠近闸极的那薄薄一层半导体产生「转性」,因此形成了通道。

所以这个通道绝对不像BJT那样是大水管1条,而是1片薄薄的导电层而已,因此以前的水电工们对MOSFET重要课题是很头痛的,若是你在30年前提到MOS这种推动力不足的东西可以跑到1GHz,科学家和水电工们肯定要笑你痴人说梦的。

不过FET也有一个绝大的好处,就是我们在闸极加上控制电压时,理论上不需要流出任何电荷到晶体心,所以控制电流理论上接近于零(实际上当然不可能,会有一堆漏电流产生),所以在芯片晶体数暴增的今天,是个很好用的技术。

▲MOS半导体导通示意图

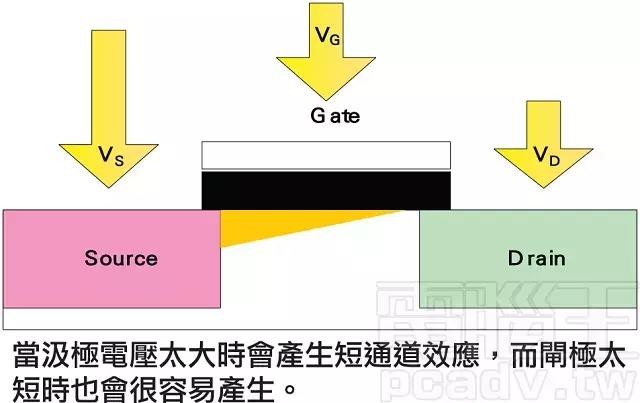

夹止

请参考MOS通道形成图,通道由于来自源极和汲极的电压差吸引,并不会变成平行于闸极的完整平面,而是一端宽一端窄的情况,当变窄的那部分小到会阻碍电流的地步时就称为夹止。

MOSMOS

只是MOSFET 的简称,没什么意义,大家常常都喜欢叫小名,因为比较好叫,通常我们讨论晶体管提到MOS是没什么问题的。但是如果要讲到午餐吃什么也用MOS 的话,应该是指卖汉堡的。

薄薄的一层,问题却很大

回到近5年来的现况,这薄薄一层的MOS导电通道推动力不大,为了仍要达到高频、省电、低热量、减少面积等等目的,半导体厂内的水电工们可是伤透了脑筋。还好在近来电子显微镜以及各类测量技术越来越进步,我们也渐渐了解到MOS通道形成有什么限制,又有什么副作用等等问题。尤其在现今半导体制程已经缩小到了30nm以下的境界,有许多问题是不断发生的,也因此开发新材料或新型结构的晶体管就成了各家厂商努力的目标。

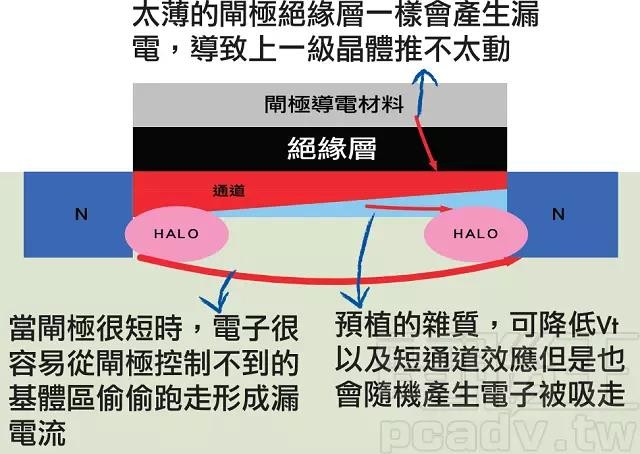

难题1 漏电流

理想的MOS晶体管除了少许拉动闸极电容的电流以及送往下一级的推动电流外,是不该有任何额外电流的,凡是超出这个范畴的电流都算漏电流。漏电流对于强调高速省电的现代产品是个大伤害。而且就微观的情况来看,其实晶体管内部有许多效应会导致漏电流,漏电流的流向也不固定,有从闸极漏走的,有从源极漏走的,而有些漏电流只有在导通时产生,有些则无论何时都在漏。尤其当晶体管愈做愈小,这些现象就会愈明显,用30nm以下的晶体管想要完全控制好电流方向而不漏出,简直就像用竹篮子装沙而不外漏一般地困难!

难题2 推动力不足

短通道效应和漏电流在某些层面是相关的,其中短通道效应主要是因为形成通道的条件太超过,造成夹止后可导电的面积变小,反而造成一种导通不良。原本我们希望加在闸极的电压愈大,能导通的输出电流就快速增大,没想到反而卡住没什么变动,这对晶体性能是很糟糕的事。如果不处理的话对于时脉上限是会有很大的影响。(好吧,至少对于喜欢加压超频的宅男有影响)

当闸极长度仅有30nm以下,短通道效应相当容易发生,和以往40奈米以上的情况有很大的不同,所以也成了一大难题。

难题3 面积问题

我们平常说的30nm制程,一般是指闸极的长度等于30nm,而当推动力不足时就要增加晶体管的宽度,那如果把闸极的长度由60nm减少成30nm,但是宽度却非得由100nm大增至300nm时,所占的面积不就更大了吗?那真的一切都白搞了,所以面积和推动力问题都是要处理的。

难题4 省电性和性能问题

由于寄生电容的影响,晶体管就算没有漏电流也会在运作过程中吃掉能量,好比闸极的电压在拉升或拉降时就会吃掉电流,吃愈多愈不好推,也造成开关速度变慢。

▲短通道效应:通道提早缩水了

闸极、源极

三极管的原理就是闸极的电压只要稍稍变大,输出端(源极)就会有很大的增加,而闸极只要没有输入,输出端也应该马上停止输出。

▲改良型MOS半导体结构

评论