基于数字移相的高精度脉宽测量系统及其FPGA实现

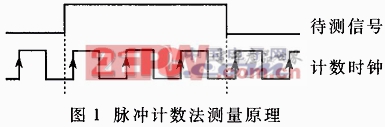

在测量与仪器仪表领域,经常需要对数字信号的脉冲宽度进行测量.这种测量通常采用脉冲计数法,即在待测信号的高电平或低电平用一高频时钟脉冲进行计数,然后根据脉冲的个数计算待测信号宽度,如图1所示.待测信号相对于计数时钟通常是独立的,其上升、下降沿不可能正好落在时钟的边沿上,因此该法的最大测量误差为一个时钟周期.例如采用80MHz的高频时钟,最大误差为12.5ns.

本文引用地址:https://www.eepw.com.cn/article/195763.htm

提高脉冲计数法的精度通常有两个思路:提高计数时钟频率和使用时幅转换技术.时钟频率越高,测量误差越小,但是频率越高对芯片的性能要求也越高.例如要求1ns的测量误差时,时钟频率就需要提高到1GHz,此时一般计数器芯片很难正常工作,同时也会带来电路板的布线、材料选择、加工等诸多问题.时幅转换技术虽然对时钟频率不要求,但由于采用模拟电路,在待测信号频率比较高的情况下容易受噪声干扰,而且当要求连续测量信号的脉宽时,电路反应的快速性方面就存在一定问题.

区别于以上两种方法,本文提出另一种利用数字移相技术提高脉宽测量精度的思路并使用FPGA芯片实现测试系统.

1 测量原理

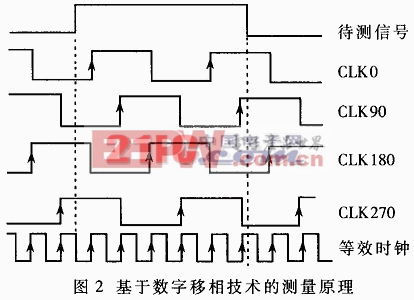

所谓移相是指对于两路同频信号,以其中一路为参考信号,另一路相对于该参考信号做超前或滞后的移动形成相位差.数字移相通常采用延时方法,以延时的长短来决定两数字信号间的相位差,本文提出的测量原理正是基于数字移相技术.如图2所示,原始计数时钟信号CLK0通过移相后得到CLK90、CLK180、CLK270,相位依次相差90°,用这四路时钟信号同时驱动四个相同的计数器对待测信号进行计数.设时钟频率为f,周期为T,四个计数器的计数个数分别为m1、m2、m3和m4,则最后脉宽测量值为:

w=[(m1+m2+m3+m4)/4]×T (1)

可以看到,这种方法实际等效于将原始计数时钟四倍频,以4f的时钟频率对待测信号进行计数测量,从而将测量精度提高到原来的4倍.例如原始计数时钟为80MHz时,系统的等效计数频率则为320MHz,如果不考虑各路计数时钟间的相对延迟时间误差,其测量的最大误差将降为原来的四分之一,仅为3.125ns.同时,该法保证了整个电路的最大工作频率仍为f,避免了时钟频率提高带来的一系列问题.

评论