基于CPLD的多路数据采集系统的设计

3 电路的VHDL描述

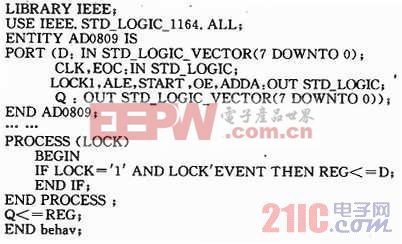

数据采集控制电路、数据处理电路均是使用硬件描述语言VHDL(Very High Speed Integrated Circuit Hatdware Description Langu-age)设计而成。例如:数据采集控制模块设计如下:

VHDL语言具有多层次的电路设计描述功能,既可描述系统级电路,也可以描述门级电路;描述方式既可以采用行为描述、寄存器传输描述或者结构描述,也可以采用三者的混合描述方式。VHDL语言的强大描述能力还体现在它具有丰富的数据类型,采用VHDL语言描述硬件电路时,设计人员并不需要首先考虑选择进行设计的器件。这样做的好处是可以使设计人员集中精力进行电路设计的优化,而不需要考虑其他的问题。当硬件电路的设计描述完成以后,VHDL语言允许采用多种不同的器件结构来实现。

4 系统的波形仿真

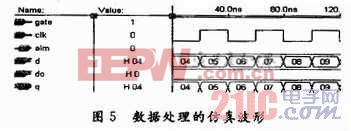

在数据处理电路中,当gate=‘1’,整个器件处于数据采集及处理模式,选择不同的工作方式,即fun值,可实现不同的数据处理,当do为O时,其波形仿真如图5所示。从仿真波形中可以看出输入数据等于输出数据,在通过输出运放,使输出值增大2倍,从而使输出数据为输入数据的2倍。

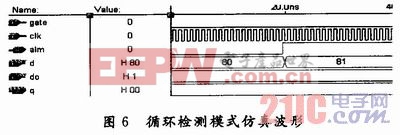

在数据处理电路中,当gate=‘0’,整个器件处于循环检测的模式,当输入数据超出预设值时就进行报警,即alm=‘1’,当无输入值大于预设值时,就进行循环检测。其波形仿真如图6所示。

5 结语

设计了基于CPLD的多路异步数据采集系统,系统中使用状态机控制数据的采集,使用ADC0832进行数/模转换。同时利用CPLD强大的数字处理功能和高密集成的特点,降低了硬件的成本,简化了电路设计,并配合软件增加了系统的灵活性和可扩充性,具有很好的经济效益和社会效益。

评论