基于DSP的抖动测量的方案

2.2 数字化的抖动测量的优点本文引用地址:https://www.eepw.com.cn/article/194930.htm

a 具有更宽的带宽和更低的噪声,因为它不需要时钟恢复。

b 具有更宽的带宽和更光滑的频率响应,因为数字相位探测器将每个NRZ沿以时间标记(不需要对模拟脉冲作平均处理)。

c 具有更低的抖动噪声,因为数字时间标记不受噪声的影响。

d 增益误差率只有0.01%,因为信号处理是完全数字化的。

e 动态范围超过4000UIp-p,同时保持0.01UI的分辨率。

f 测量时没有延时,因为不使用锁相环信号去获取时钟。

3 数字式抖动测试仪的研制

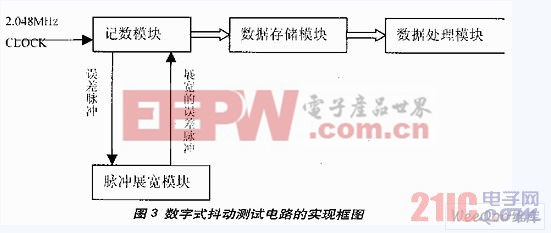

数字式抖动测试仪的基本要求是完成对2.048MHz的锁相时钟进行相位抖动测试,具体要求按ITU-TG.823建议执行。设计方案采用数字方法测试抖动。数字抖动测试方法中关键的就是计数器的设计,本设计选用的计数器的计数时钟频率为100MHz。但是为了保证测试抖动的精度要求,对于100MHz记数产生的误差信号,专门设计了误差脉冲展宽电路,以提高测试精度。图3给出了数字式抖动测试仪的功能框图。

研制的抖动测试仪主要包括以下模块:时钟记数、脉冲展宽、数据存储、数据处理。其中除了脉冲展宽模块是模拟电路外,其余的3个模块都是数字电路,所以该设计是一种数字与模拟的混合电路。在设计中,考虑到算法的复杂性和灵活性,开发时间的紧迫性以及系统的要求,选用了德州仪器(TI)的TMS320F206。

评论