基于SOPC数据采集与控制系统的设计

2 硬件设计

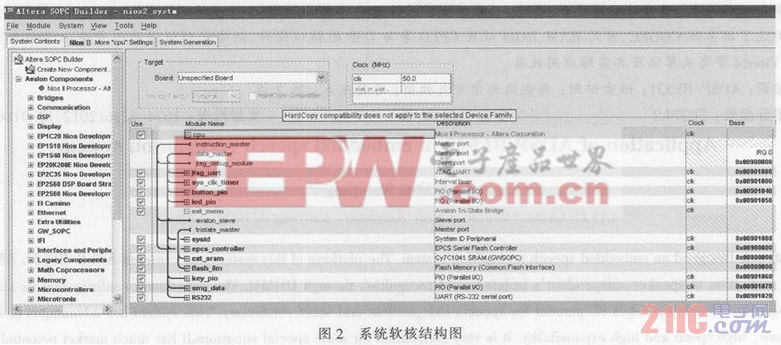

利用SOPC技术结合VHDL硬件描述语言,在FPGA芯片内部设计硬件控制部分;再加上外围电路就构成了整个系统的硬件电路。FPGA内部各模块利用Altera公司提供的Quartus II开发软件和其中集成的SOPC Builder系统开发工具来设计。SOPC Builder支持Nios II CPU的配置,并支持设计者在其提供的IP库中,根据系统设计需要选择相应的接口模块,加入到NiosII系统中,将这些设计在Quartus II中编译并生成sof格式文件后,下载到FPGA芯片中就形成了SOPC的嵌入式系统硬件平台。

2.1 NiosII软核处理器

本设计选择的处理器是Altera公司推出的第二代嵌入式NiosII软核处理器。Nios II处理器系列是一种面向用户的,可以灵活定制的通用RISC(精简指令集架构)嵌入式CPU。Nios以软核的方式提供给用户,并专为在Altera的FPGA上实现作了优化,用于SOPC(片上可编程系统)集成,最后在FPGA上实现。

它的外设可以灵活选择或增删,可以自定制用户逻辑为外设,可以允许用户定制自己的指令集,使用Nios加上外部的Flash、SRAM即可构成一个嵌入式处理器系统。构建的软核处理器如图2所示。本文引用地址:https://www.eepw.com.cn/article/193299.htm

2.2 串行通信接口

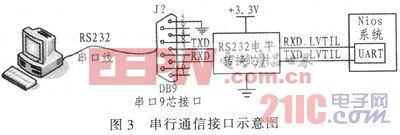

串行通信接口芯片选用MAX3232,由电平转换芯片完成从LVTTL电平到RS232C电平的转换,如图3所示。

2.3 LED数码管、发光二极管

8位数码管显示数据,通过接收的数据控制点亮相应的二极管。数码管显示译码在FPGA内部实现。发光二极管通过限流电阻直接接在FPGA的I/O口上。

2.4 Flash、SRAM存储器、键盘

系统片外FLASH选用AM29LV065DU,片外SRAM选用UM611024A;作为运行Nios II的FLASH和SRAM。十个按键KEY0-KEY9直接与FPGA芯片的I/O口连接。

评论