基于FPGA器件的Sobel算法实现

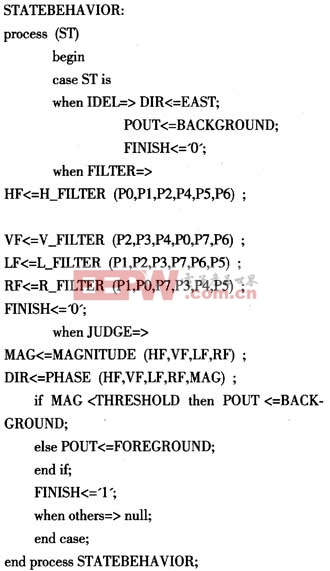

以上全部代码中使用的数据类型和函数均已在PIXEL_PROCESSING.vhd文件中定义,因此,设计时只需在本VHDL文件中使用use子句将其作为设计库中的包进行引用即可,其代码如下:本文引用地址:https://www.eepw.com.cn/article/192125.htm

use work.PIXEL_PROCESSING.all;

通过采用以上VHDL语言行为域进行描述,即可完成基于Soble算法的图像边沿检测模块的设计。

3仿真分析

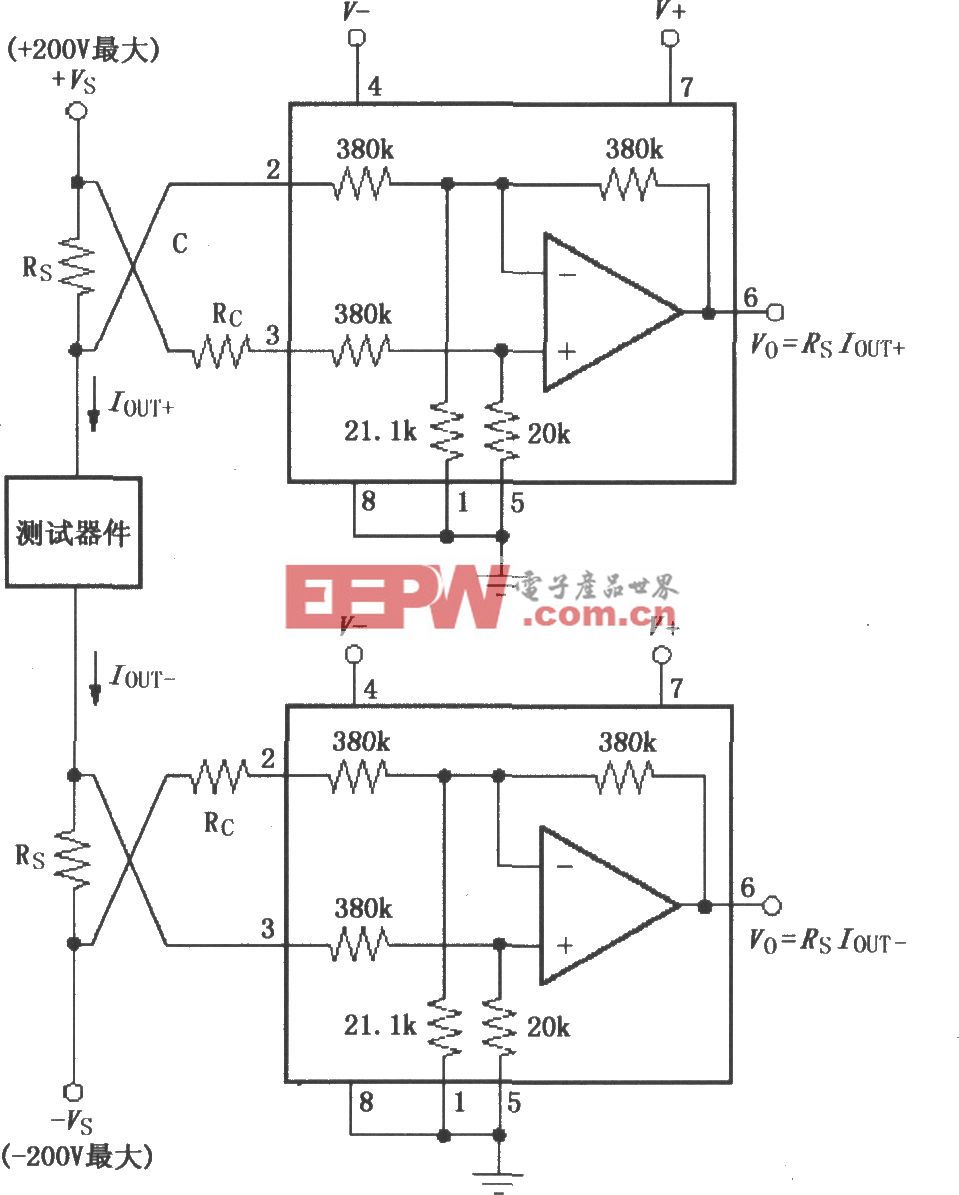

采用两个数据窗可对系统进行功能仿真。从图5所示的仿真时序中可以看出,两个时钟周期可完成一个数据窗的处理,第一个时钟周期生成滤波值VF、VH、VL和VR,第二个时钟周期生成幅值MAG并产生判决结果POUT。当用40 MHz时钟时,若能以此时钟二分频的速度连续产生数据窗,则处理一个像素只需50 ns,也就是说,处理一个800×600的图像只需24 ms。此时,系统处理速度的瓶颈已不在边缘检测模块,而由其它模块,如像素窗的生成速度所决定。

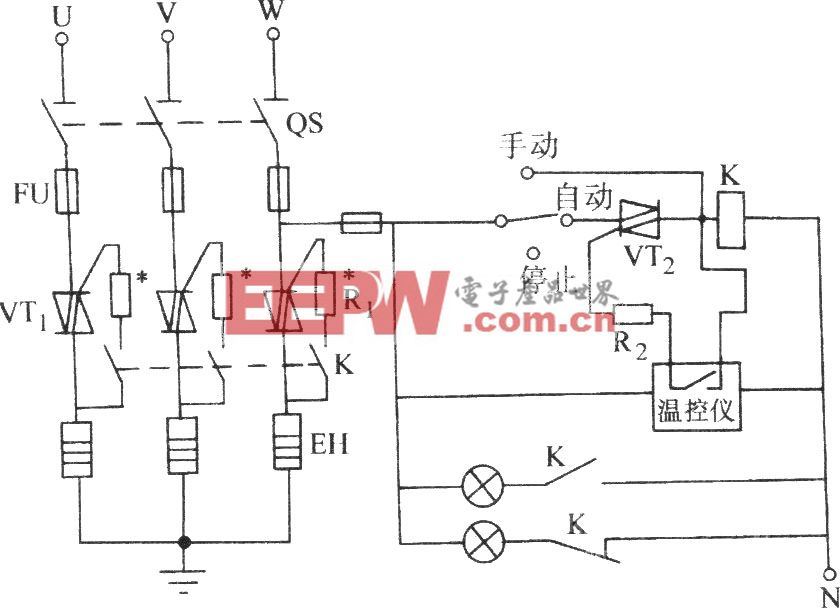

除此之外,第二个时钟周期所产生的有效检测结束信号(FINISH)既可以作为前端模块的数据窗发送信号,也可以作为后端模块的检测结果接收信号。该信号对模块间的协同工作具有重要的意义。

4结束语

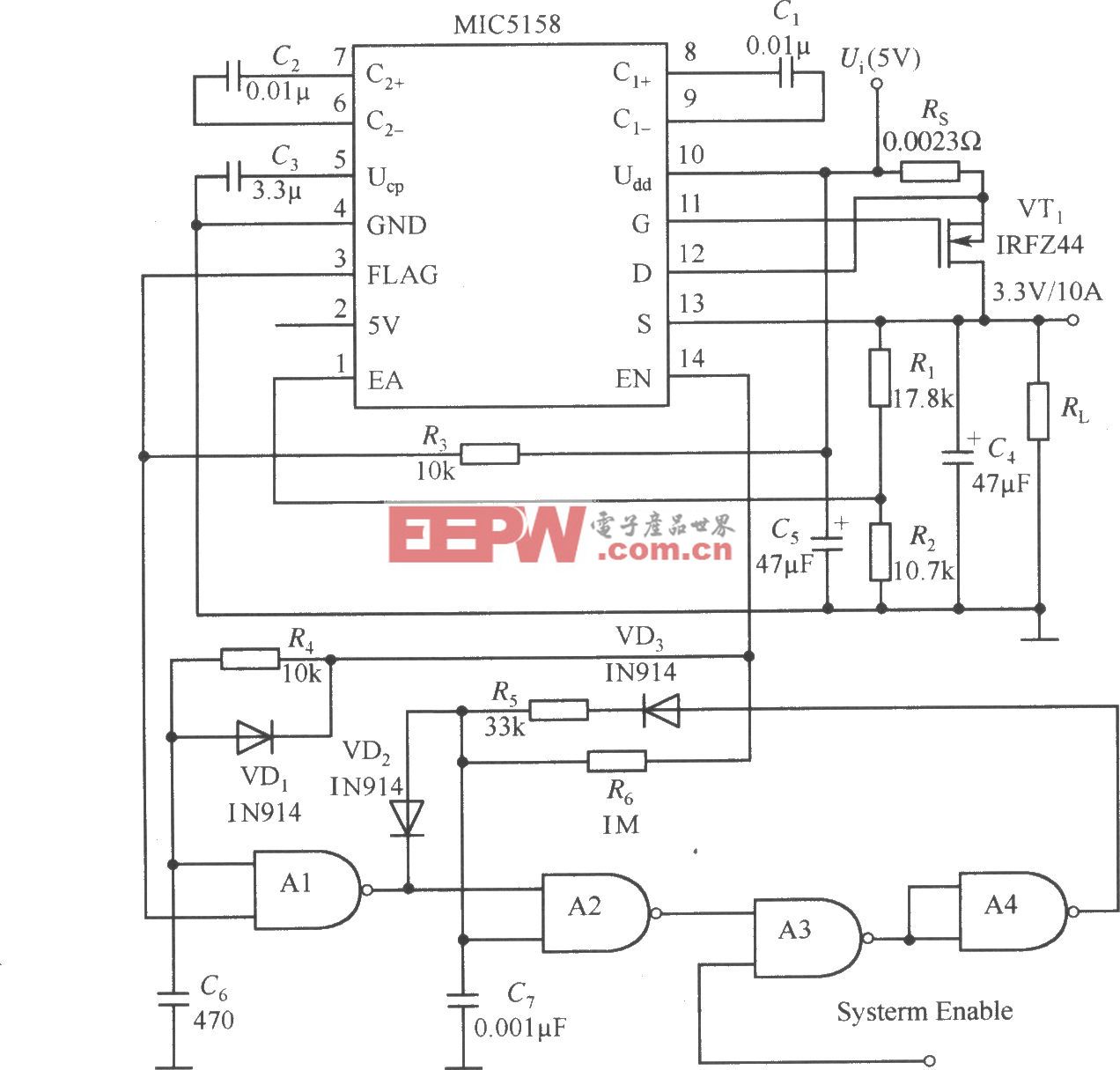

采用FPGA器件实现Soble算法的图像边缘检测具有设计过程简单,处理速度快等优点。该方法将前端的像素窗生成模块、后端的图像处理模块以及其他功能模块集成至同一FPGA器件中,从而大大提高了系统的集成度。

评论