基于FPGA的电子琴动态录音与回放系统的设计

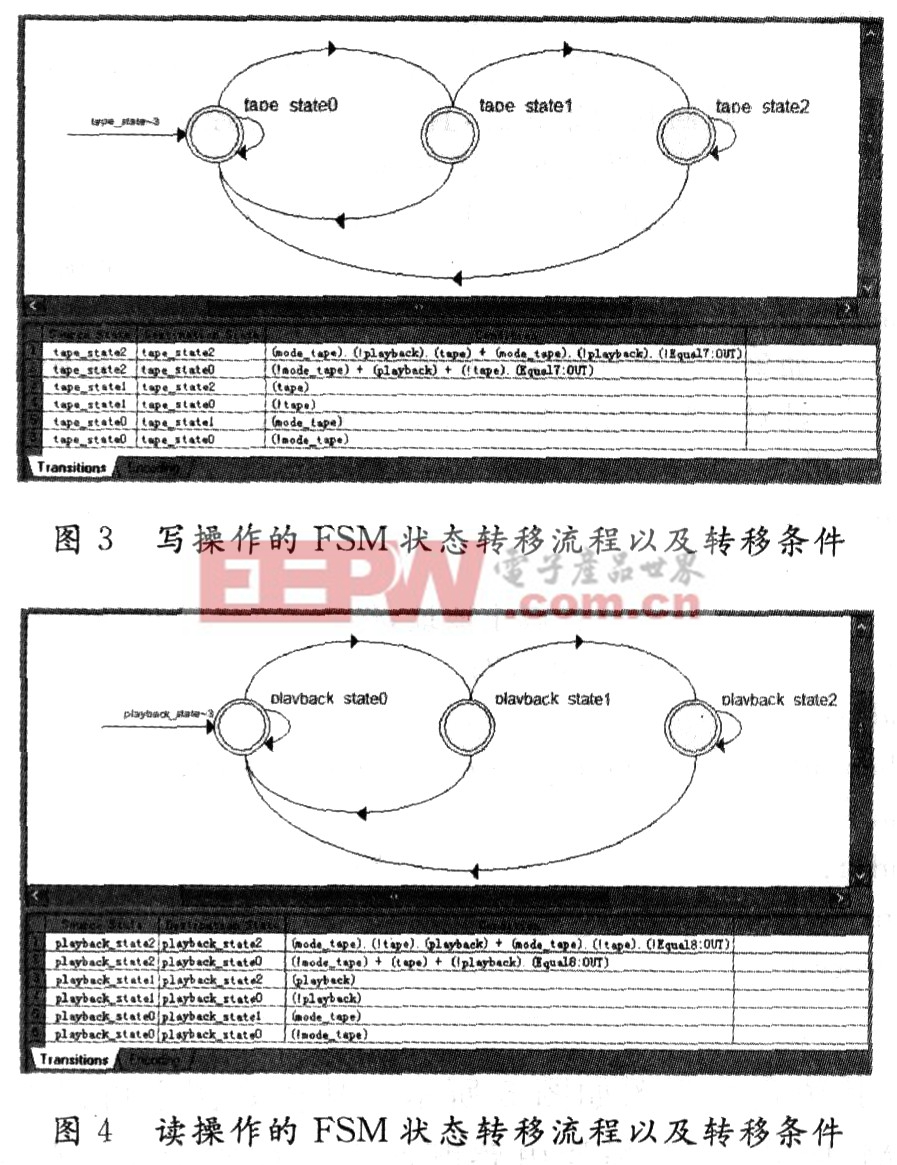

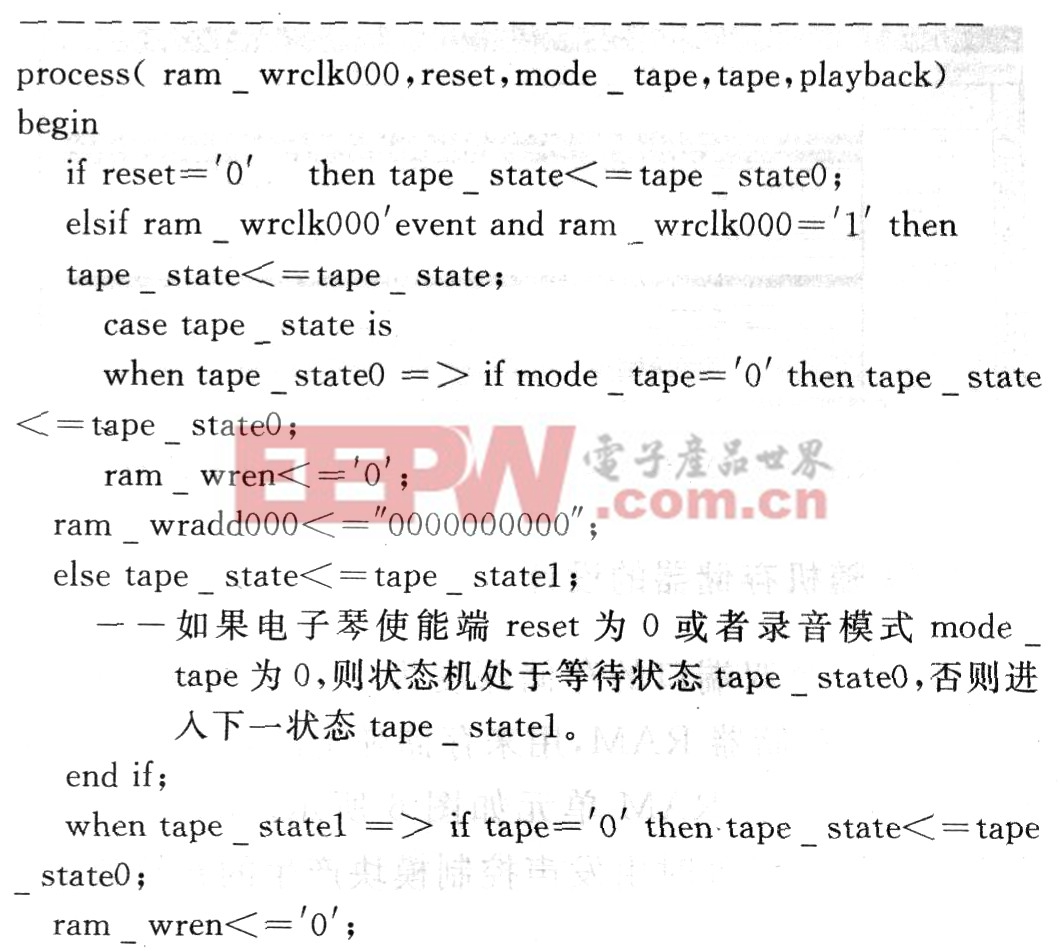

写操作的FSM状态转移流程以及转移条件如图3所示;读操作的FSM状态转移流程以及转移条件如图4所示。

本文引用地址:https://www.eepw.com.cn/article/192067.htm

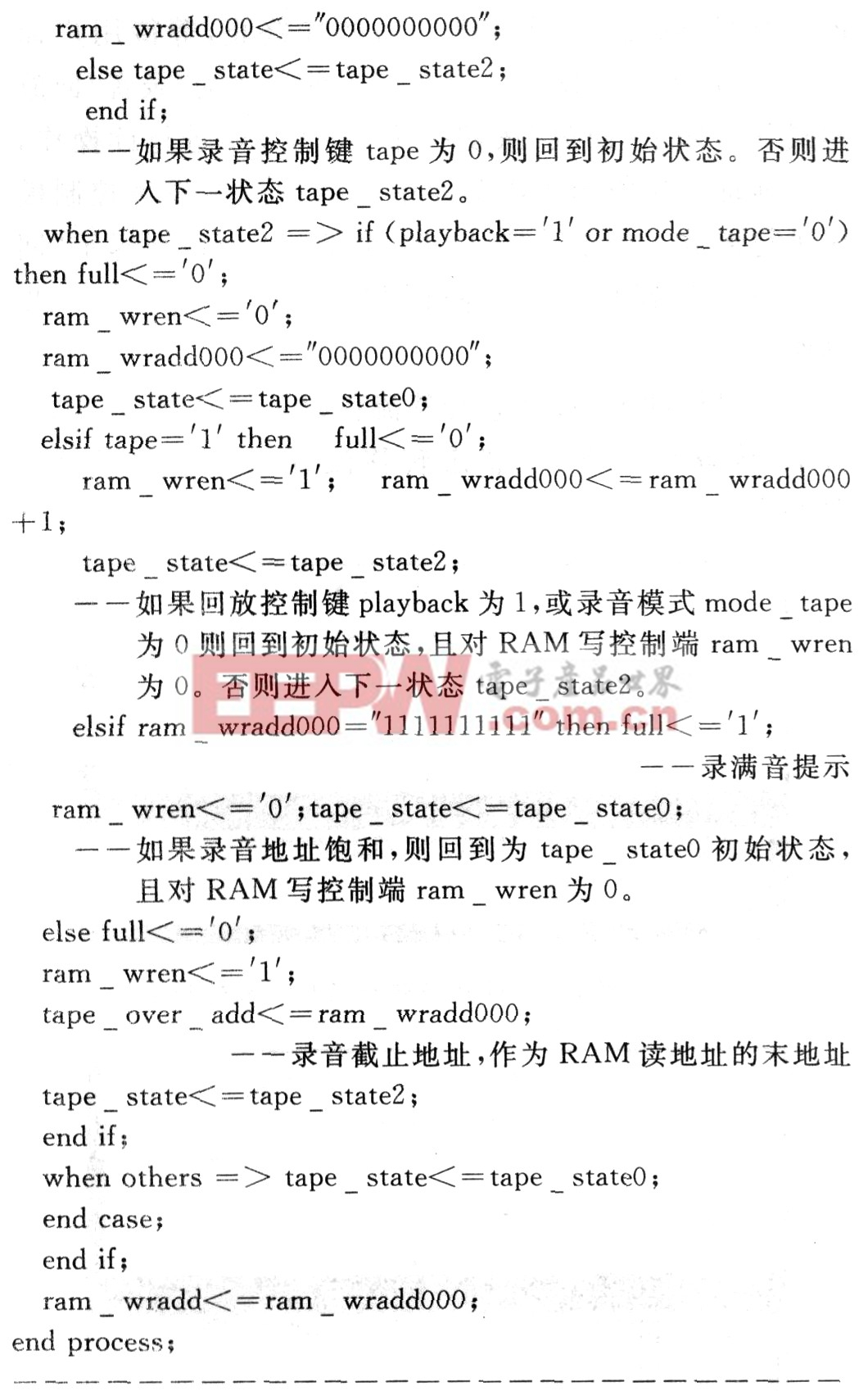

本文引用地址:https://www.eepw.com.cn/article/192067.htm用状态机对RAM进行读写控制的部分源程序如下:

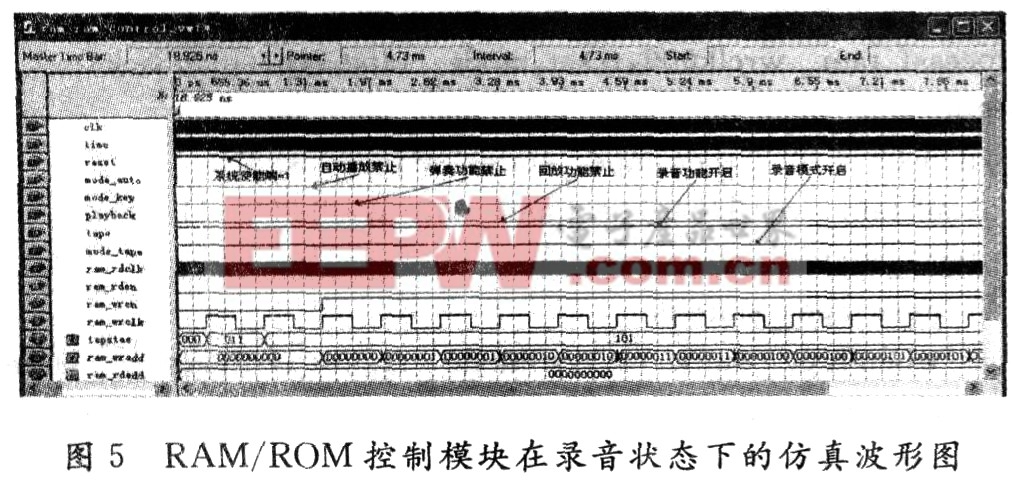

其仿真波形图如图5所示。从仿真图上可以看出,RAM/ROM控制模块电路既产生了控制RAM存储器的时钟ram_wrclk信号,也产生了相应的控制RAM的使用使能信号ram_wren和写入地址ram_wradd。

3 RAM随机存储器的设计

评论