基于FPGA的RCN226绝对式编码器通信接口设计

DSP在每个电流环周期发送一个有效的begin信号,20μs之后,码盘信号接收模块将接收到的数据存入FPGA内部双口RAM的A口中,并按顺序排列成16位数据的形式,然后向DSP发送end信号,表示一次通信结束,DSP接收到中断之后从FPGA的双口RAM的B口中读取数据,完成一次通信, DSP的连接如图3所示。本文引用地址:https://www.eepw.com.cn/article/191929.htm

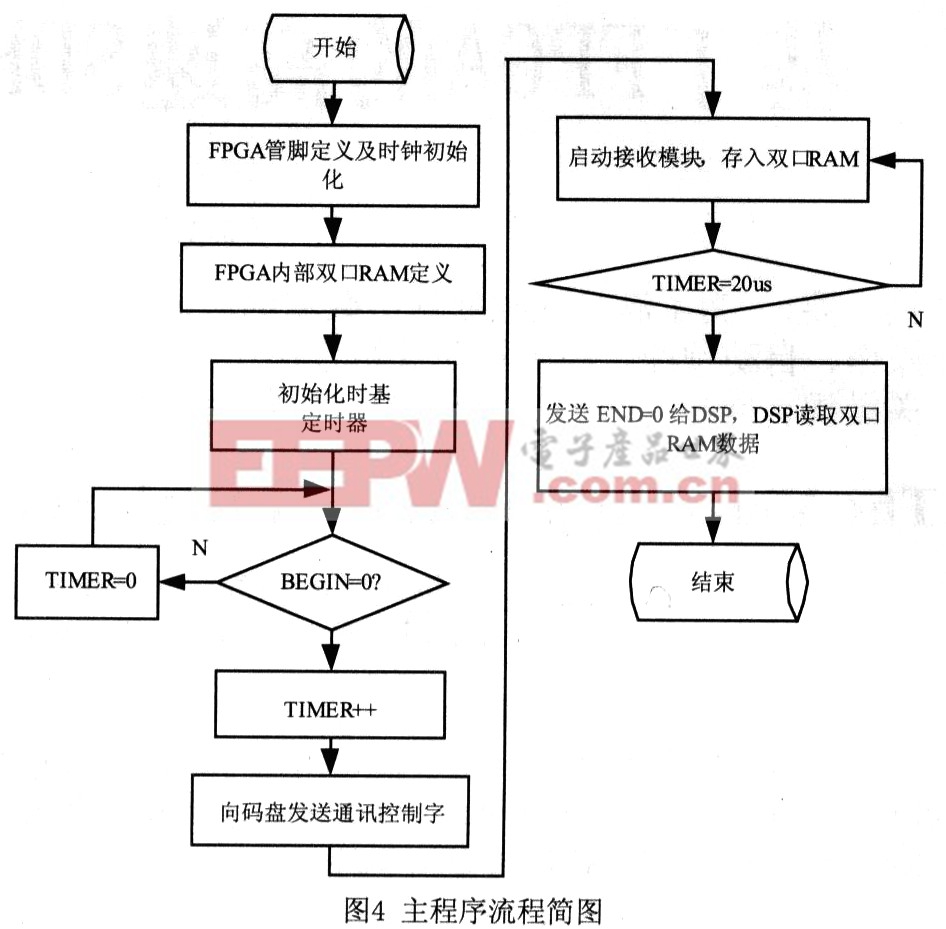

在本接口的研发过程中,对FPGA的开发采用Altera公司的Quartus II 5.1集成环境,硬件描述语言为VHDL语言。图4为主程序流程图。

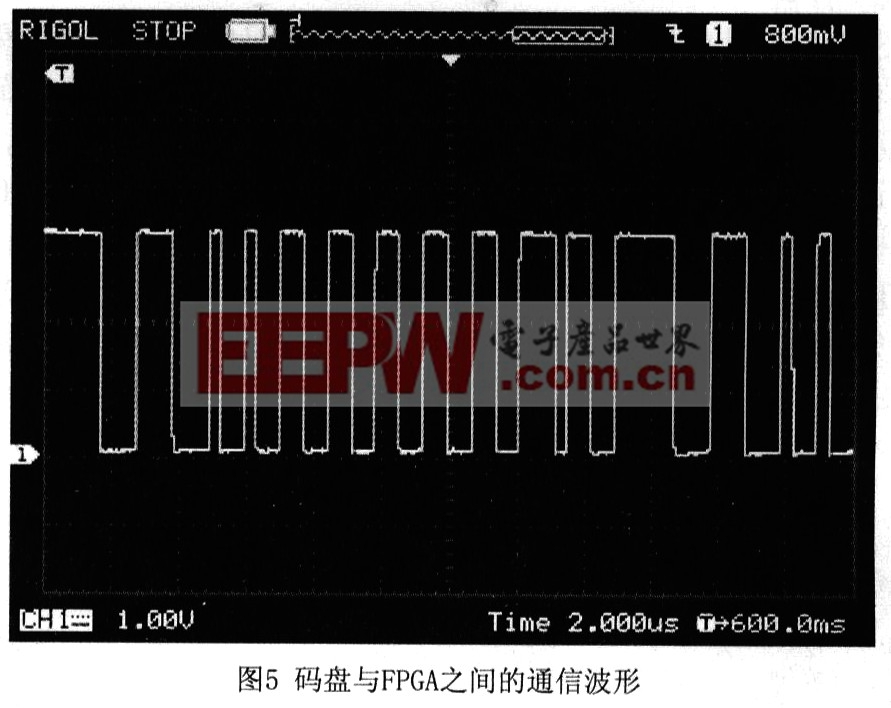

图5为码盘与FPGA之间的通信波形,从位置信号可以看出该接口工作正常。 |

3 结束语 |

fpga相关文章:fpga是什么

伺服电机相关文章:伺服电机工作原理

评论