基于CPLD的函数信号发生器设计

3.3 软、硬联调

该系统软件与硬件之间的联系不是十分紧密,一般是软件计算完毕后,将数据存入ROM,CPLD读取单片机系统的数据,进行运算、逻辑分析,从而产生波形。因此在软、硬件都基本调通的情况下,系统的软、硬件联调难度不大。输出波形的频率范围测试数据如表1所示。本文引用地址:https://www.eepw.com.cn/article/191767.htm

由表1可以看出,在频率稳定度方面,正弦波、方波、三角波在带负载的情况下均十分稳定,这正体现了DDFS技术的特点,输出频率稳定度和晶振稳定度在同一数量级。脉冲波占空比的调试如表2所示。

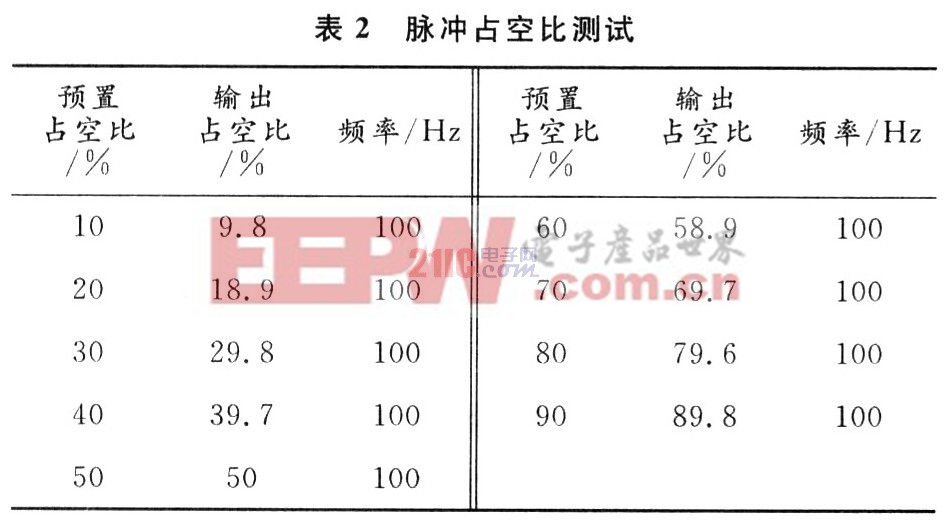

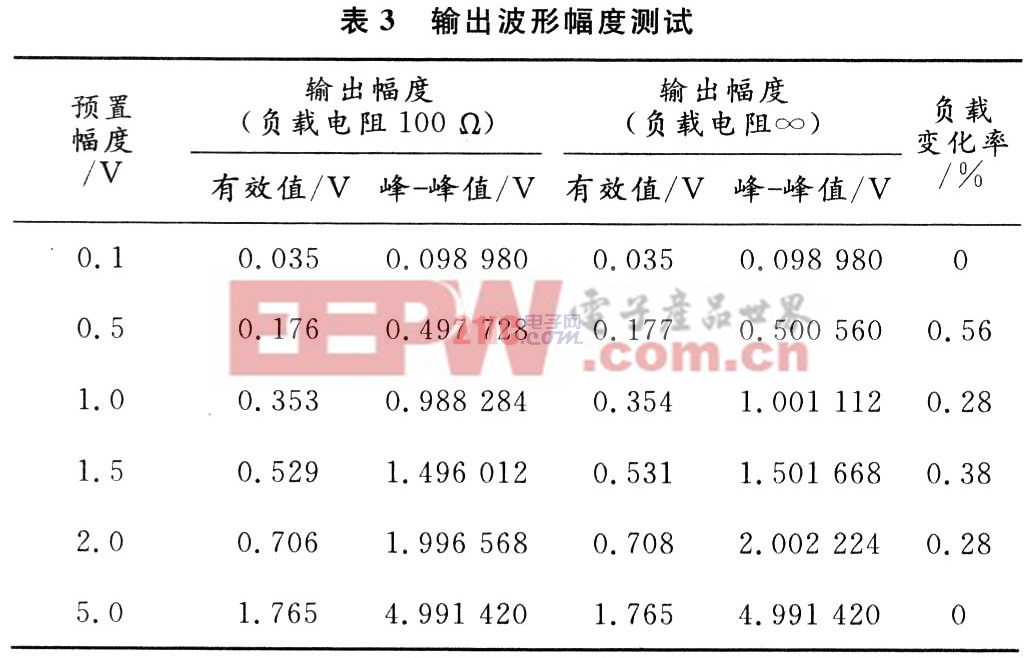

由表2可以看出,占空比可以在10%~90%范围内预置。在20 kHz正弦波条件下测得的输出波形幅度数据如表3所示。

由表3可见,电压稳定度方面,在电压的绝对值和预置值之差及带负载和不带负载的情况下,输出电压之差均小于±1/100。

4 结 语

系统采用DDFS技术和单片机控制CPLD的方法,实现了常用的正弦波、方波、三角波和占空比可调的矩形波,频率范围为20 Hz~20 kHz。利用LED显示波形的类型、频率和幅值,并具有输出电路保护功能。经实际调试,该系统的频率范围宽,步进小,幅度和频率的精度高。

评论