基于信号完整性分析的高速PCB设计

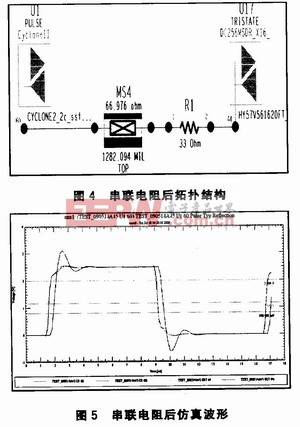

串联电阻后振铃现象得到了很好的解决,实际上这个解决方法叫阻抗匹配,阻抗在信号完整性问题中占据着极其重要的地位。

2.2 串扰

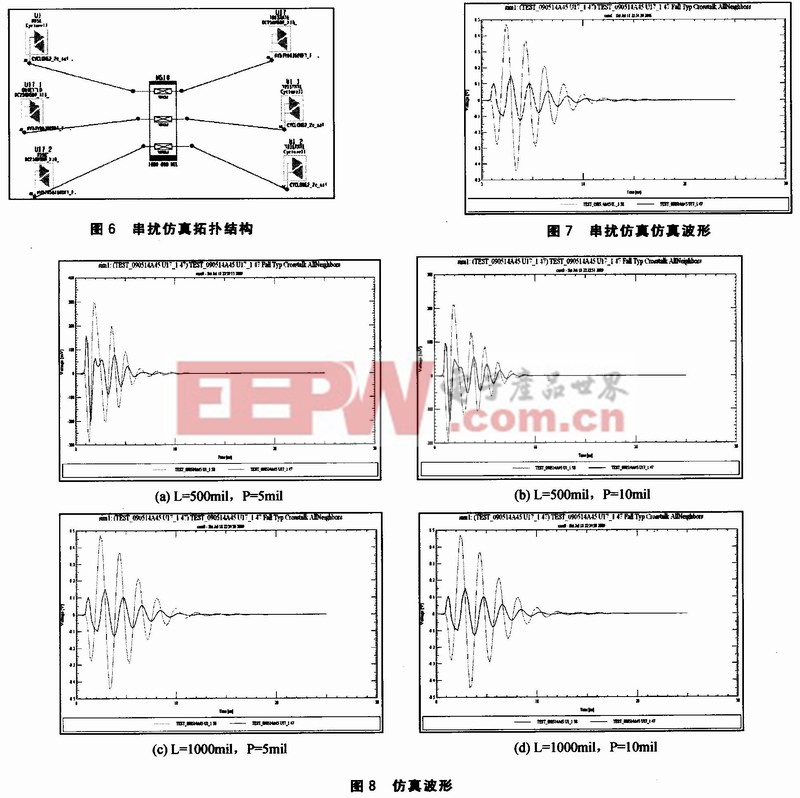

提取SD_DQlO(连接Cyclone II的59引脚和HY57V561620的45引脚),SD_DQll(连接Cyclone II的58引脚和HY57V561620的47引脚),SD_DQ-l2(连接CycloneII的57引脚和HY57V561620的48引脚)这三个网络来做它们之间的串扰仿真。其中,SD_DQll作为被攻击网络,SD_DQlO和SD_D-Ql2作为攻击网络。它们的拓扑结构和仿真波形如图6、图7所示(传输线的并行耦合长度L=1000 mil,间距P=5 mil)。

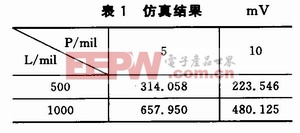

仿真波形如图8所示。由图7可以看出串扰对于被攻击网络的影响还是很大的,串扰值Crosstalk=657.95 mV串扰的大小与传输线的并行耦合长度L和间距P有关,耦合长度越短,间距越大,串扰就越小。仿真结果如表1所列。

因此,制作PCB时,在允许的情况下要尽可能减小不同性质信号线之间的并行长度,加宽它们之间的间距,改变某些线的线宽和高度。当然,影响串扰的因素还有许多,比如电流流向、干扰源信号频率上升时间等,应综合考虑。

结语

在本次控制单元高速PCB设计中,运用功能强大的Cadence软件,从制作原理图、PCB布局到高速仿真分析,取得了较好的效果。依据SPEECTRAQuest仿真分析所得到的合理的拓扑结构和布局布线,使电路板工作正常。这种设计方式大大缩短了硬件调试时间,提高了工作效率,节约了设计成本。

评论