基于VHDL语言的几种消抖电路的设计

主要程序结构如下:

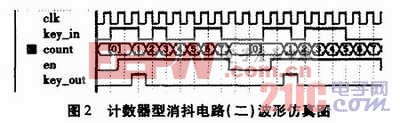

图2是N为7的波形仿真图。在计数器状态为0时,key_in有按键操作,计数器开始连续计数直到计数器状态为0;计数器状态为1-7时,key _in任何操作对计数器工作无影响,计数器在状态为1时,输出一个单脉冲,脉冲宽度为1个时钟周期。本文引用地址:https://www.eepw.com.cn/article/191239.htm

该设计方案的特点是能很好消除按键抖动产生的连续脉冲,对按键时间没有要求,缺点是在计数器状态为0时,遇到干扰、噪音等时会有输出,从而产生误操作。

2 D触发器型消抖电路

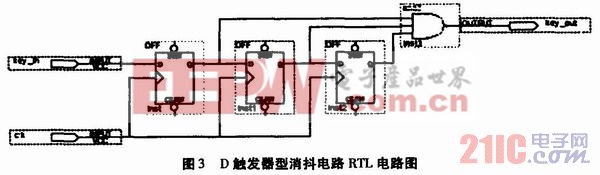

D触发器型消抖电路设计了三个D触发器与一个三输入与门。三个D触发器串行连接,其Q输出端分别与三输入与门的输入端连接,D触发器型消抖电路RTL电路如图3所示。

评论