FPGA控制下面阵CCD时序发生器设计及硬件实现

在CCD时序发生器模块中,输入为时钟和复位信号,以及两路同步信号VD和HD;输出除了CCD驱动所需的10路信号外,还包括SHP和SHD两路用于相关双采样的电路以及暗像元、哑像元驱动时序。

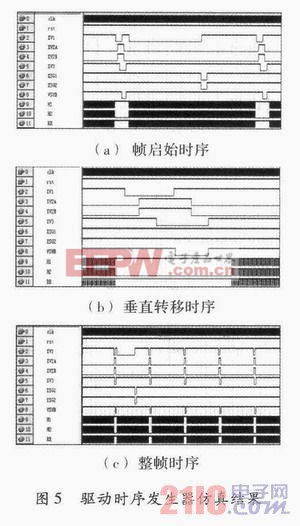

在对VHDL语言描述的时序发生器进行编译后,对驱动时序发生器进行功能仿真,仿真结果如图5所示。本文引用地址:https://www.eepw.com.cn/article/191097.htm

通过对FPGA芯片程序的下载。将功能模块集成于CycloneII系列芯片EP2C8T144C8N中。该时序发生器顶层模块程序资源占用率仅为3%。

4 硬件实现以及测试结果

CCD信号采集驱动电路硬件部分主要分为两个部分,即CCD驱动电路和偏置电压的设计。

4.1 偏置电压电路

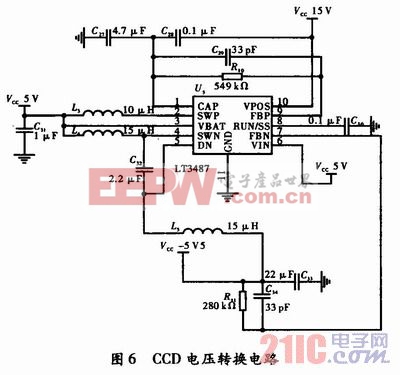

对ICX098BQ的数据手册进行分析,Hφ1、Hφ2水平移位驱动工作电压峰峰值为3.3 V,分别为-3.3~0 V和0~3.3 V,Vφ1、Vφ3垂直转移工作电压为5.5 V(-5.5~0 V),Vφ2A、Vφ2B为三电平,工作电压为(-5.5 V、0 V、+15 V)。因而需要-5.5 V和+15 V作为CCD垂直驱动时序的工作电压。偏置电压+15 V和-5.5 V采用Linear公司生产的LDOLT3487获得,偏置电压产生电路如图6所示。

评论