PCB板电磁兼容设计关键良好的时钟电路设计方案

2.2 时钟频率对辐射的影响

假设有2个时钟信号,幅度都为1 V,上升时间都为3.33 ns,重复频率为30 MHz和90 MHz,根据上面的傅里叶变换可以得到2个时钟信号的频谱分布,如图2和图3所示。

2.3 时钟频谱的比较

从图1可以看出,时钟谐波干扰尤其是高次谐波干扰的强度会随着上升和下降时间的降低而大大加强,2 ns上升时问的时钟的高次谐波比4 ns上升时间的对应谐波高出1~2倍。

当上升下降时间相同时,周期T(或者基频f)的高低对时钟产生的高次谐波干扰的影响非常大,图2和图3分别是重复频率30MHz和90MHz,上升时间都为3.33 ns,幅度为1 V的梯形时钟波谐波干扰的大小。从图中可以看出,2种时钟在270 MHz的谐波干扰,90 MHz时钟在270 MHz(3次谐波)的谐波干扰比30 MHz时钟在270 MHz(9次谐波)的谐波干扰高出15 dB左右;再比较90 MHz时钟在810 MHz(9次谐波)的谐波干扰比30MHz时钟在810 MHz(27次谐波)的谐波干扰高出12 dB左右。

因此在进行时钟系统设计时,在条件允许的情况下优先选用较低的时钟频率,比如在设计以太网的PHY芯片时既有采用125 MHz外部时钟的也有采用25 MHz外部时钟的,如果在其他技术条件允许应优先选用外部时钟为25 MHz的芯片,而且在各方面技术条件都满足的情况下优先选择上升和下降时间比较长的时钟或者时钟驱动电路。

在PCB板上实现时钟电路的电磁兼容设计主要从下面的几个方面来考虑:时钟晶振及其驱动器的电源处理;在PCB板上晶振及其驱动器的下面做局部的覆铜处理;时钟信号线的布线;时钟信号的端接和滤波等。

3.1 电源设计

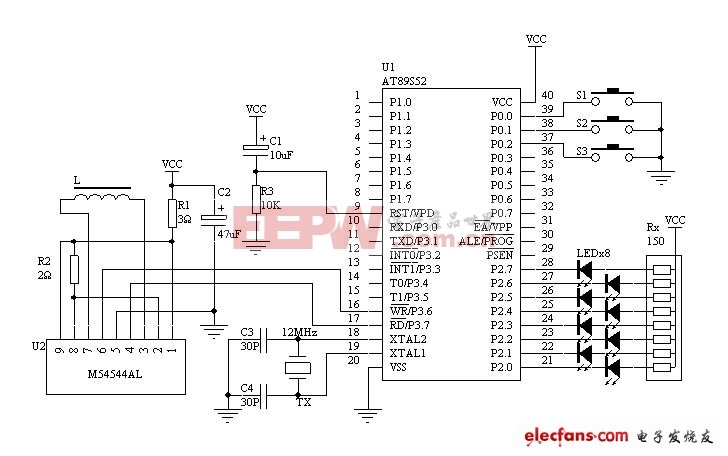

当时钟电路的输出同时发生状态变换时,会对电源系统产生较大的瞬态电流,或灌电流,为了避免时钟芯片对单板电源系统的冲击,抑制单板电源的电磁干扰,就需要对时钟电源部分进行滤波和隔离设计。其设计原理图如图4所示。

3.2 铺铜及布线设计

晶体振荡器内部的电路会产生射频电流,如果晶体是金属外壳封装的,直流电源脚是直流电压参考和晶体内部射频电流回路参考的依据。不同的晶体(CMOS,TTL,ECL等)内部产生的射频电流对金属外壳的辐射大小不同,如果晶体金属外壳不与大的地平面连接,则不能将晶体金属外壳上大的瞬态电流泻放到地平面上。

评论