基于FPGA的交通信号灯控制系统

2 系统状态分析

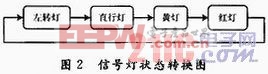

对设计要求进行分析可知,主、支干道交通灯变化顺序应如图2所示。本文引用地址:https://www.eepw.com.cn/article/190117.htm

状态转换如表1所示。

3 系统结构设计

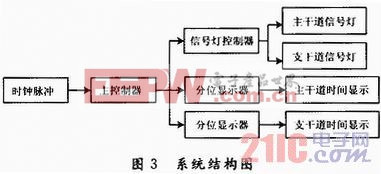

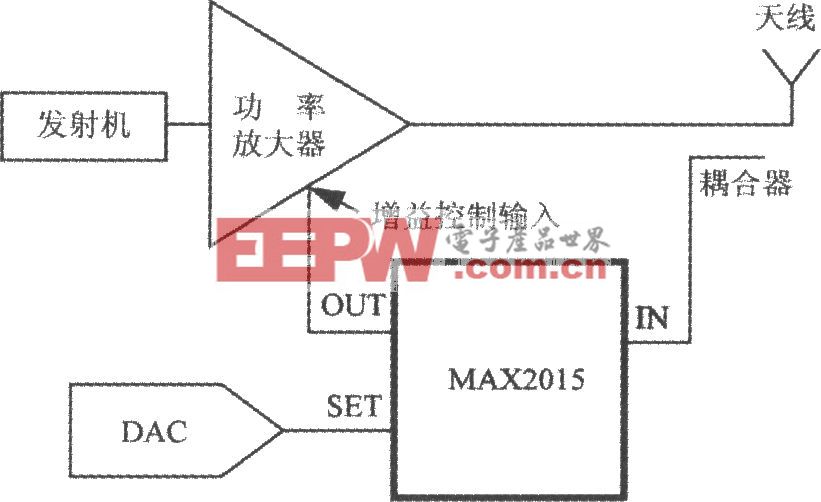

根据要求,系统结构图设计如图3所示。时钟脉冲由分频器对晶振脉冲进行分频产生。主控制器接收时钟信号,并据此进行状态转换,同时输出各状态的时间。信号灯控制器根据主控制器产生的状态量对主、支干道信号灯进行控制。由于主控制器输出的时间信号为实数类型,因此还需设计分位器将其转换为两组BCD码分别送至数码管显示。

4 VHDL设计实现

为便于系统实现,采用VHDL语言对各个模块进行设计。主控制器为一计数器,输入信号为秒脉冲,以70为一个周期,计数到1后,在下一个时钟信号来到时,计数器复位,开始下一轮计数,如此往复。系统复位信号reset可使计数器从任意状态复位至状态S0,并重新开始计数。下面是主控制器的VHDL文件。其中clk和rst是时钟和复位信号,state表示当前状态,seg7a、seg7b分别表示主、支干道倒计时时间,temp为内置变量。

fpga相关文章:fpga是什么

评论