基于FPGA的宽带数字信道化接收机的设计

现代电磁信号环境越来越复杂密集,要求电子战接收机必须具有很宽的处理带宽、高灵敏度、大动态范围、多信号并行处理和大量信息实时处理的能力。而数字信道化接收机不仅可以较好地满足上述要求,还可实现监视信道内信号的全概率截获。

本文引用地址:https://www.eepw.com.cn/article/190021.htm数字信道化过程是宽带数字接收机的核心,目前广泛采用基于多相滤波的数字信道化结构。这种结构先用高速的模数转换器(A/D)进行数据采样,得到的高速数据流经抽取降低数据速率后进入多相滤波器组,该滤波器组是由一个原型滤波器调制到多个支路。现场可编程门阵列(FPGA)中丰富的乘法器、锁存器及数字信号处理算法IP核等资源,可以非常灵活地实现宽带数字信道化接收处理算法。本文采用基于多相滤波器的结构实现了一种高效高速的宽带数字信道化接收机,并在Altera公司的EP3SE110F1152C4上综合实现,输出载频、相位信息。

1 信道化接收机的基础理论

1.1 信道划分

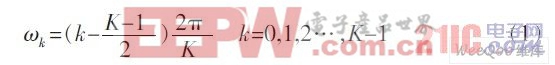

为建立实信号多信道接收机的数学模型,首先,对实信号的数字谱作如下信道划分:

式(1)中,ωk为第k信道的归一化中心角频率;K为划分信道数。图1给出对应k=8时,实信道的频谱分配情况。需要指出的是由于实信号的频谱是对称的,所以只有4个独立的信道。

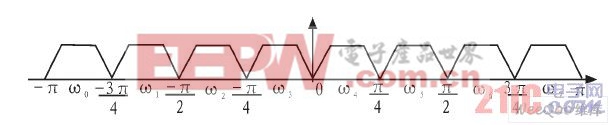

图1 实信号的信道划分示意图

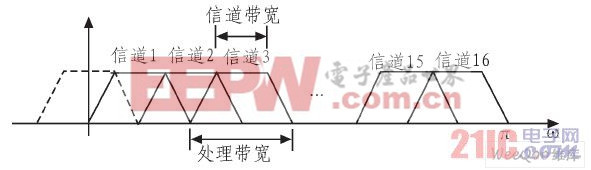

采用上述方法进行信道划分有些频点无法识别,为确保整个覆盖带宽内无盲区,信道的划分选择相邻信道50%交叠,即扩大每个信道的处理带宽,如图2所示。

图2 50%交叠的信道划分示意图

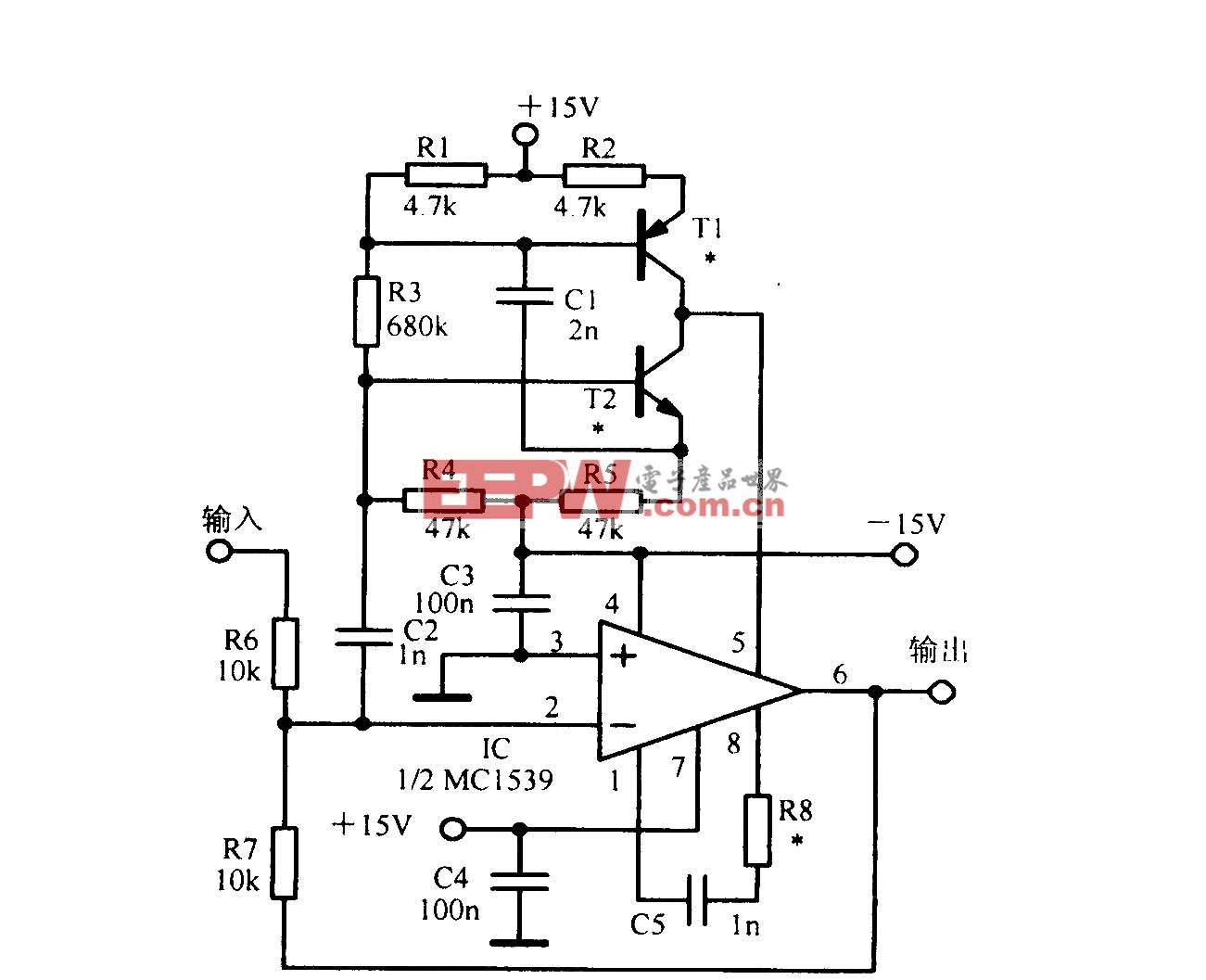

1. 2 多相滤波器组结构

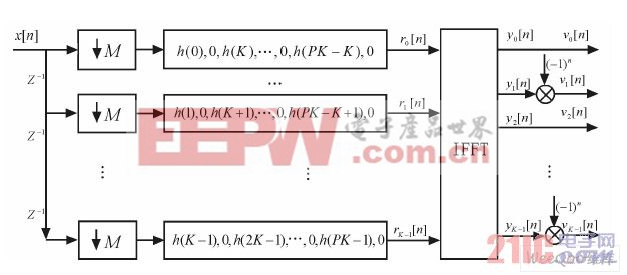

本文采用高速高效数字信道化结构完成信道化接收,其数学模型如图3所示。

图3 高速高效数字信道化接收机结构图

图3中K为系统划分的信道数,M为每个信道的抽取倍数且K=FM。H(n)为原型低通滤波器的单位冲击响应,K个带通滤波器都是通过该原型滤波器调制生成的,即均匀滤波器组的多相滤波分量。

评论