基于FPGA的高速多路视频数据采集系统

3 系统软件设计

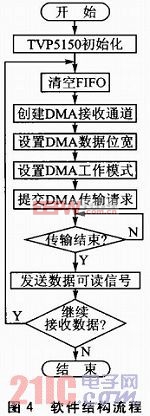

本方案软件部分主要为TVP5150芯片初始化、DMA控制器的配置等。软件结构流程如图4所示。本文引用地址:https://www.eepw.com.cn/article/190015.htm

4 实验结果

为检验高速多路视频数据采集系统的图像采集效果,系统外接4路摄像头同时采集图像数据,在实际视频数据采集过程中,多路视频图像显示连贯流畅。将存储在SDRAM中的图像数据读取后,通过后期融合算法,融合成环境平面图像,实际多路图像采集融合效果如图5所示。

结语

本文基于FPGA设计了一种高速多路视频数据采集系统,该系统通过外接视频扩展板连接多个视频摄像头,通过在FPGA内部构建视频解码模块,能够对每路视频数据并行解码,提高要求实时性的多路数据采集的效率,并可在不更改硬件设计的前提下对编码格式的数据采用不同的解码模块。SOPC系统的自定义FIFO接口能够高速缓存视频数据。通过DMA IP Core的使用,可减少Niosll软核CPU读取低速I/O接口数据所占用的时钟周期,提高整个系统的工作效率。

评论