基于FPGA的高精度时差测量系统设计

3 时差测算单元设计

3.1 设计思想

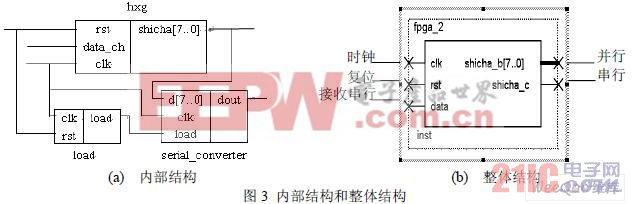

FPGA 作为时差测算单元的核心器件,主要完成相关匹配、并/串转换、接口控制等功 能,经过VHDL 编程生成的内部结构和各个模块综合以后的整体结构如图3 所示。

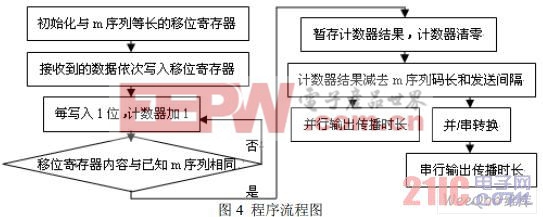

其中,hxg 模块通过互相关的方法测算出不同路径的传播时长,采用8 位并行输出; serial_converter 模块把hxg 模块的结果转换成串行输出;load 模块作为serial_converter 模块 的使能输入,当load 有效时并行数据被存储到移位寄存器中。程序流程图如图4 所示。

3.2 实现结果

以 5 级的m 序列为例,反馈系数为45(八进制),初始状态为10000,得到31 位的m 序 列为1000010010110011111000110111010。码速率为1Mbps,固定发送间隔为100000 码元, 即100ms,总共发射4 组m 序列,因此参考图2 可知能够测得3 个传播时长。下图中的并行输出结果均用十进制显示。整体结果和局部放大结果如图5 所示,仿真结果表明并行结果 与串行结果完全一致。

评论