基于FPGA的高精度时间数字转换电路设计

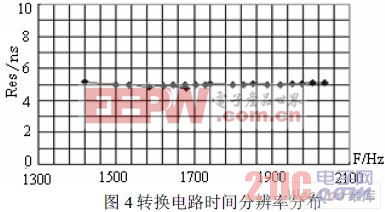

由该 TDC构成的脉宽测量电路在 Cyclone EP1C3Q240C8芯片实现,系统外部时钟 25Mhz,PLL设置倍频因子 8,由 SP1641B信号发生器提供固定的被测脉冲频率 F,时间分辨率 Res的分布如图 4所示,测试数据表明 Res在 4.9-5.1ns之间,理论值为 5ns。

测量和仿真数据表明该电路能达到纳秒级时间分辨率,逻辑资源占用少,可在低密度芯片上实现作为专用测量电路使用,或在高密度芯片上作为功能模块嵌入到特定功能的片上系统(SOC)中;该 TDC电路的转换速度也在纳秒级,使该电路适用于实时数据采集及高速数据处理系统。精度可调也是该设计一大特点,移位脉冲的工作频率决定了该转换系统的转换精度,通过时钟管理单元可以产生不同频率的移位时钟,从而测量精度可以根据具体需要进行适当调整。

3结束语

本基于 FPGA的时间数字转换电路设计在占用较少芯片资源的前提下,实现了很高的测量精度,工作时数据转换速度也在纳秒级;本设计电路接口简单可作为独立的功能电路使用,亦可作为功能模块 IP核[8]方便地嵌入到其他系统实现特定功能。基于 Altera芯片的时序仿真和硬件测试表明了该方法的可行性和准确性。

评论