数字化幅度调制电路的实现

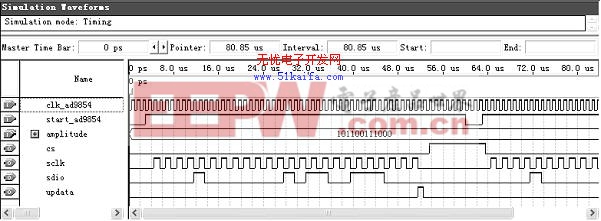

图3 串行传输时序图

AD9854的控制芯片还需要去控制将待传输的语音信号转换为数字信号的模拟/数字转换器的工作。由于可编程逻辑器件具有并行工作的特点,使得其对模拟/数字转换器的控制工作和向AD9854的数据传输可以采用流水线的方法进行。设计中采用ALTERA公司的FPGA器件EP1C3,这种FPGA器件的端口电压支持3.3V,这与AD9854芯片相同;同时它具有104个用户可使用的输入/输出管脚,足够整个系统使用;再有就是它的内部也具有基于锁相环的时钟倍频电路,降低了对外部时钟在工作频率方面的要求。

采用有限状态机(FSM)的时序电路模型,使用VHDL实现的AD9854芯片数据接口代码格式如下:

IF (start_ad9854 = '0') THEN --启动信号有效,状态清0

current_state = 0;

ELSIF (start_ad9854 = '1') THEN --启动信号无效,状态机工作

IF (clk_ad9854'EVENT AND clk_ad9854 = '1') THEN --AD9854串行2线数据传输模块时钟有效

CASE current_state IS --根据有限状态机状态进行分支处理

・・・・・・

WHEN 24 => --当前状态24

current_state = 25; --下一个状态25

cs = '0'; sclk = '0'; sdio = amplitude(11); updata = '0';

--模拟/数字转换结果位11数据

WHEN 25 => --当前状态25

current_state = 26; --下一个状态26

cs = '0'; sclk = '1'; sdio = amplitude(11); updata = '0';

--串行时钟有效,位11数据写入

・・・・・・

WHEN 50 => --当前状态50

current_state = 50; --下一个状态50

cs = '1'; sclk = '0'; sdio = '0'; updata = '0';

・・・・・・

图4 AD9854芯片数据接口仿真波形图

图4是实现向AD9854芯片传送模拟/数字转换结果的仿真波形图。模块时钟clk_ad9854频率选取1MHz。每个数据传送循环由启动信号start_ad9854为低电平开始,这使得当前状态为0。当启动信号变为高电平,在模块时钟的控制下依次产生所需的各个状态。在每个状态下,分别产生串行数据传送选择信号cs、串行时钟信号sclk、串行数据信号sdio和刷新信号updata。当前数据传送完成以后,状态机在最后一个状态自跳转,如代码举例中的状态50,等待下一个数据传送循环开始时的启动信号start_ad9854低电平。

5 结束语

本文作者创新点:实现了一个全数字化的幅度调制电路,并包括载波信号的产生。利用调幅收音机在整个频段内对电路的工作进行了检测,获得满意的结果。相对于模拟幅度调制电路,数字幅度调制电路具有抗干扰能力强、一致性好以及容易实现设计自动化等优点。

ALTERA公司的FPGA器件不仅提供实现逻辑电路的资源,同时也提供了大量的嵌入式存储模块。采用FPGA器件可以很方便地实现相位累加器和波形数据表,工作速率也满足要求。如果用它来实现DDS信号源,当前的主要困难为必须添加数字/模拟转换器,高速数字/模拟转换器不仅价格较高,而且它与FPGA器件之间的高速数据传送对电路板也提出较高的要求。

DIY机械键盘相关社区:机械键盘DIY

评论