9位100 MSPS流水线结构A/D转换器的设计

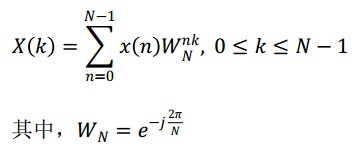

图7是采样频率为100 MHz,输入信号在幅度为2.2 V、频率为25 MHz情况下,对输出信号做离散傅里叶变换(DFT)得到的频谱图。由图可知,输入信号频率为25 MHz时无杂散动态范围(SFDR)为97.84 dB,完全满足设计要求。

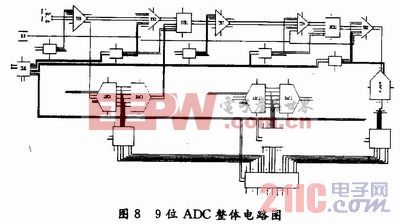

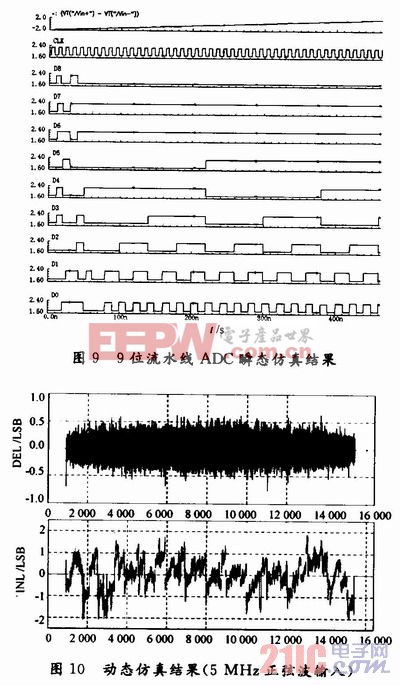

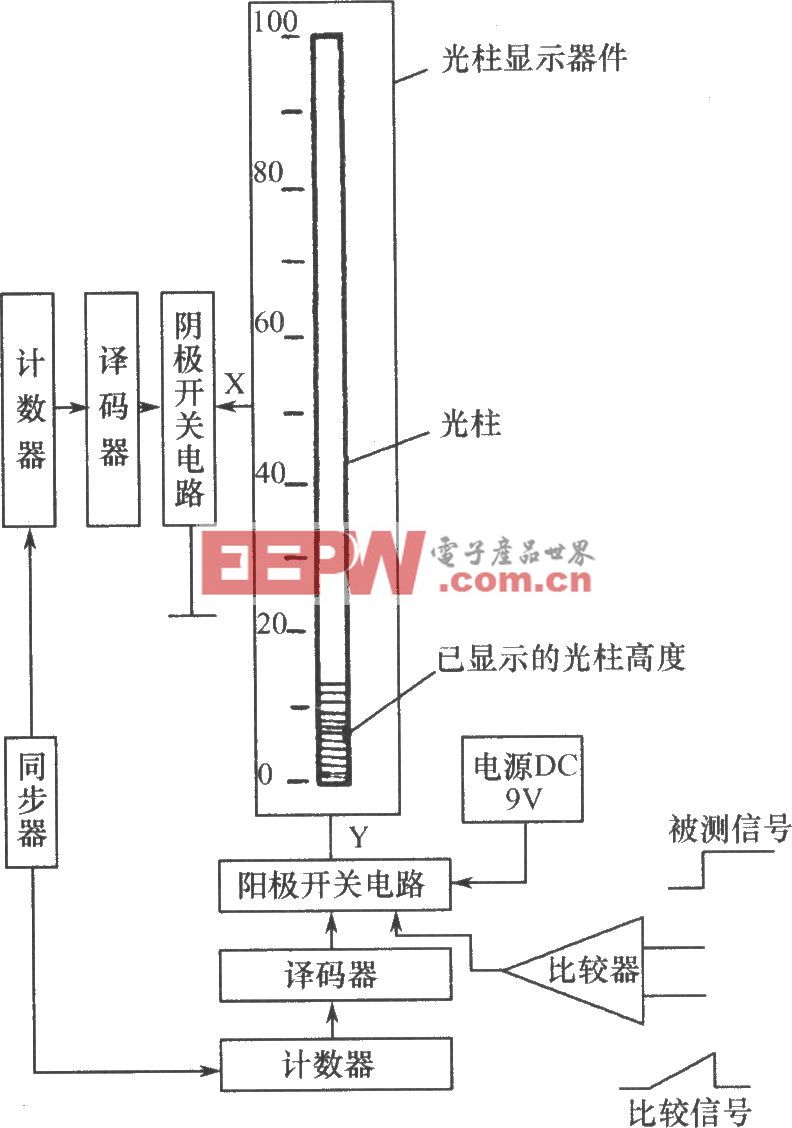

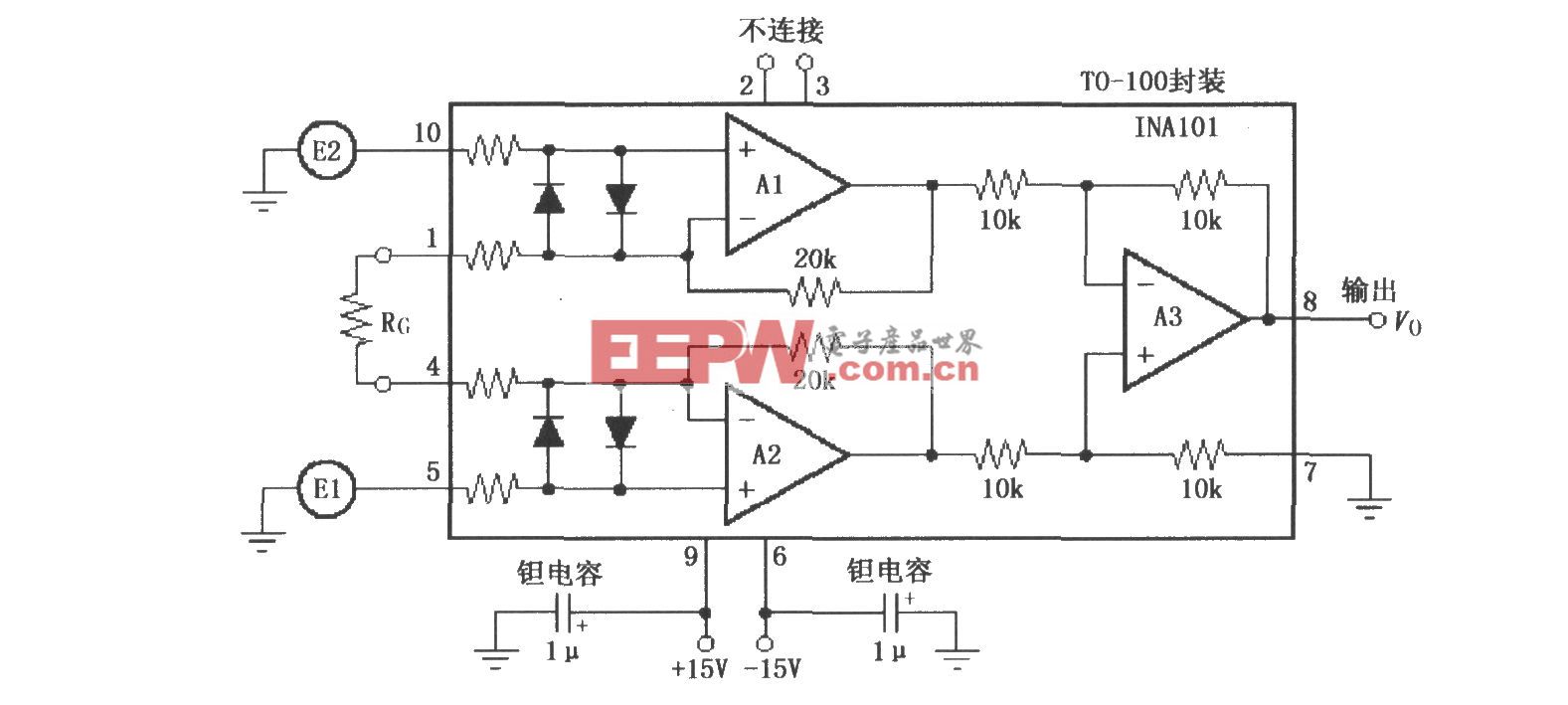

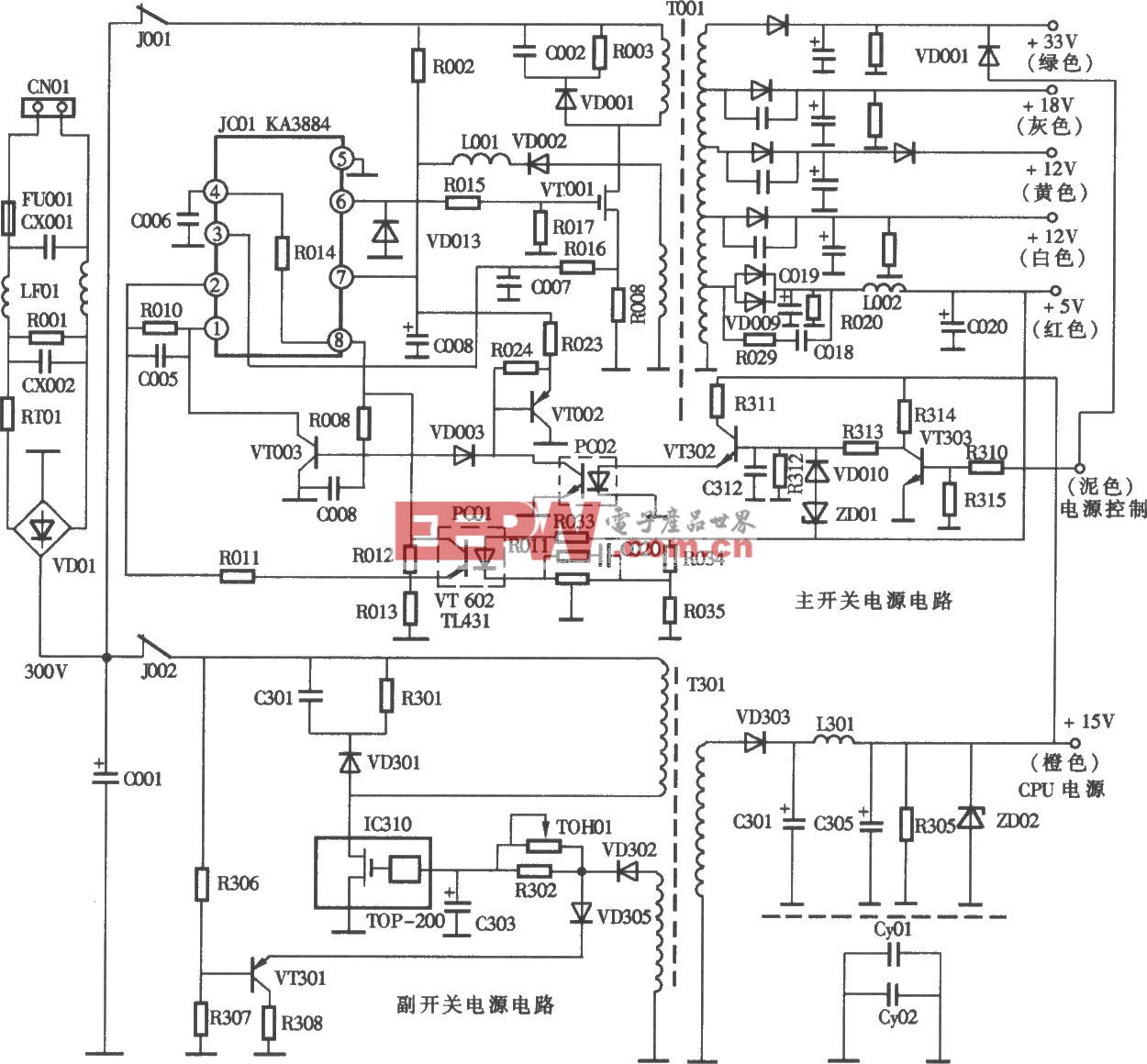

图8是9位100 MSPS三级流水线A/D转换器整体电路图,采样时钟CP频率为100 MHz,输入信号为一个上升的斜波的正弦波,峰峰值为2.2 V。图9和图10分别为A/D转换器的瞬态仿真结果和动态仿真结果。

由仿真结果可以看出,电路具有良好的线性度,在整个输入范围内鲜见误码。典型的DNL为0.7LSB,INL为2.0LSB,满足电路设计要求。

3 结语

本文设计了一个9位100 MHz低功耗流水线A/D转换器电路。该A/D转换器采用开环结构的采样保持电路提高了输入带宽,使用折叠结构子ADC,简化了电路结构,减小了芯片面积和功耗。该ADC有效输入带宽达到100 MHz。在奈奎斯特频率范围内,整个ADC的有效位数始终高于10位。在100 MHz采样频率下,电路的功耗仅为650 mW。

评论