基于CAN总线的A320模拟器硬件仿真方案研究

3 CAN节点通信接口硬件电路设计

由于驾驶舱各节点间的控制逻辑复杂,数据量大,通信频繁,故对各节点主控芯片的存储容量有较高的要求,且对CAN总线网络中数据传输的稳定性也有较高要求。选取C80C51F040作主控芯片,因其拥有4 352 B RAM以及64 KB的FLASH,满足程序应用需要。它内部集成CAN控制器,它兼容CAN技术规范2.0A和2.0B,主要由CAN内核、消息RAM(独立于CIP51的RAM)、消息处理单元和控制寄存器组成。CAN内核由CAN协议控制器和负责报文收发的串行/并行转换RX/TX移位寄存器组成。消息RAM用于存储报文目标和每个目标的仲裁掩码。这种CAN处理器有32个随意配置为发送和接收的报文目标,并且每一个报文目标都有自己的识别掩码,所有的数据传输和接收滤波都是由CAN控制器完成,而不是由CIP51完成。C8051F04O所具备的完善的CAN总线控制器和独立的CAN信息缓冲区,可以解决MCU(Micro Control Unit)与CAN总线之间串/并转换、不同节点间波特率误差的校正、以及MCU与CAN总线通信的冲突竞争和同步等问题,为CAN总线网络具有较高稳定性提供了可靠的保障。

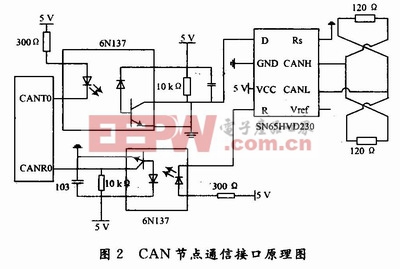

CAN总线的收发器选用TI公司的SN65HVD230芯片,该芯片正常模式下的低电流设计使得芯片的发热量小(典型数值为370μA),而且其优化的驱动器设计使得信号质量得到进一步改善;为进一步提高系统抗干扰能力,在主控芯片C80C51F040和收发器SN65HVD230之闻加入光耦6N137进行电气隔离,由于通信信号传输到导线的端点时会发生反射,反射信号会干扰正常信号的传输,因而总线两端接有终端电阻以消除反射信号,有效隔离CAN总线上的干扰信号,提高了系统可靠性。如图2所示。本文引用地址:https://www.eepw.com.cn/article/187558.htm

4 数据传输软件设计

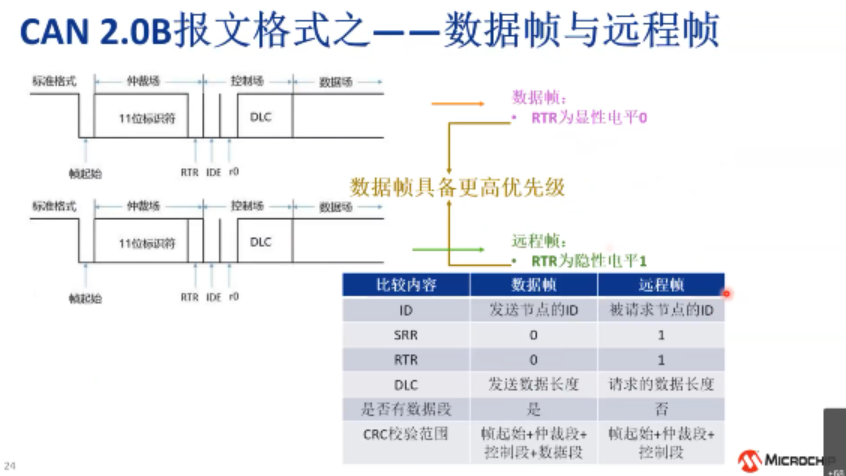

在CAN总线上发送的每一条报文都具有惟一的一个11位或29位数字ID,当发生冲突时,仲裁器就根据ID值的大小决定优先级最高的ID发送,其他的退出总线。CAN总线状态取决于二进制数0而不是1,即信号是线“与”关系:当一个节点发送1,另一个节点发送0时,其他节点接收到的是信号0。所以ID值越小,该保报文拥有的优先权越高。

评论