直流偏移校正功能与ADS58H40 PCB布局优化

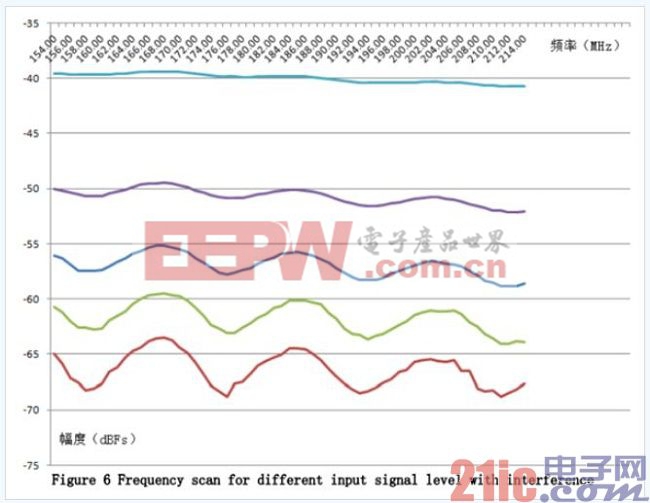

为了进一步说明码域翻转干扰的影响。用不同幅度的信号输入给 ADS58H40 进行扫频测试,将采集到的数据制图如下:

ADS58H40 的采样时钟为 245.76MHz,针对其第二奈奎斯特域的中心 60M 范围,使用 5 个功率等级进行扫频。在功率大于-40dBFs 时,由于 PCB 布局不当所引入的码域翻转干扰对输入信号影响很小(由于 ADC 前端有滤波器的关系,所以输入信号不是完全平整的)。但是随着输入信号功率的减小此干扰对输入信号的影响越来越大,在输入信号幅度低于-60dBFs 时,去除模拟输入端滤波器的影响后其引起的功率误差依然可以达到 3dB 以上。

4、针对码域翻转干扰的 ADS58H40 PCB 布局优化

为了避免码域翻转干扰耦合到 ADC 的模拟输入端,需要针对性的避免一些不当的 PCB 布局。码域翻转干扰可以通过三个途径耦合:

(1)数据输出线与模拟输入电路布局很近且平行,直接耦合。

(2)数据输出线耦合到 ADC 的时钟信号再间接耦合到模拟输入端。

(3)数据输出线耦合到 ADC 的 VCM,再通过 VCM 间接耦合到模拟输入端。

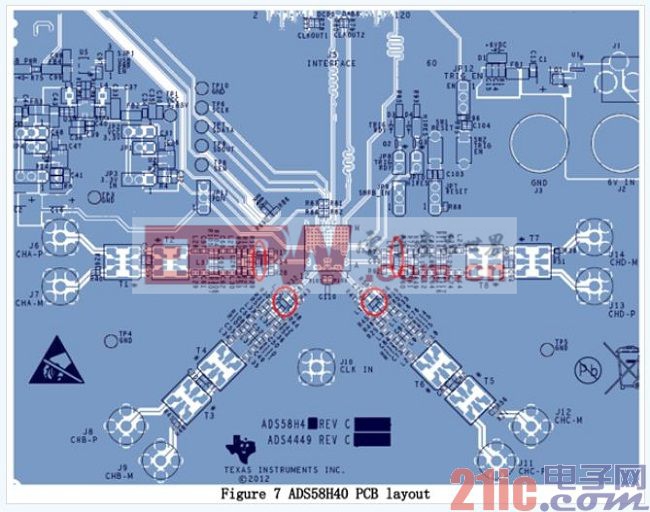

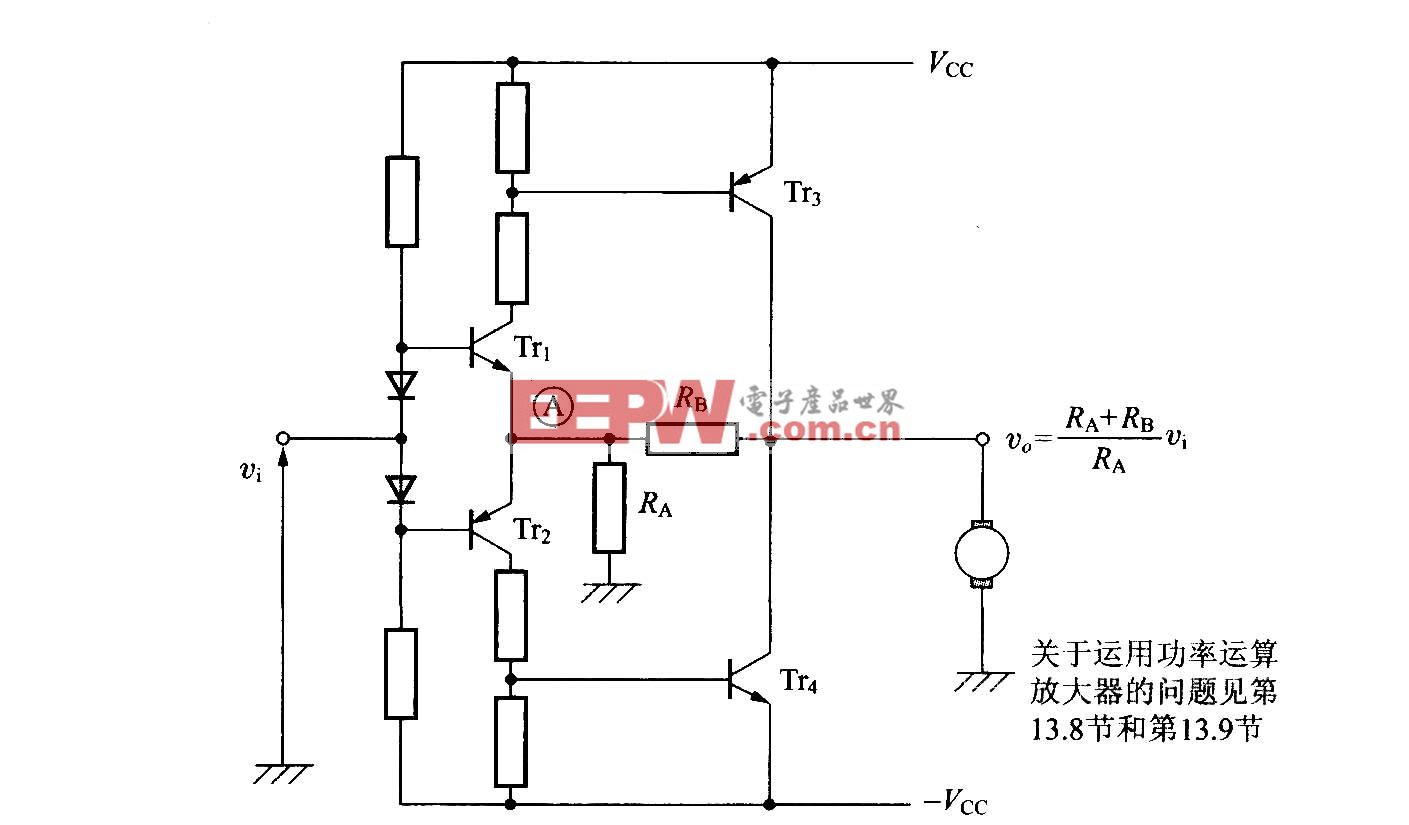

上图为 ADS58H40EVM 评估板的 PCB 布局,在基站收发信机上不会有这么大的空间来给其布局,一些走线难免会离得很近,所以针对码域翻转干扰的三个耦合途径,建议对 ADS58H40 PCB布局做出以下三个优化:

(1) ADS58H40 的数据输出 LVDS 线与模拟输入电路分开布局,不要平行或交叉。

(2) ADS58H40 的采样时钟线与随路时钟线布局尽可能的远离模拟输入端,不要与其近距离平行。

(3) ADS58H40 的 VCM 线最好通过过孔直接从模拟输入电路的差分端中间接入,如上图四个红色圈的中心。在模拟输入端 VCM 接入口必须加上对地的滤波电容。VCM 信号不要做成 VCM 电源平面,而且布局时使其尽量远离数据输出线。

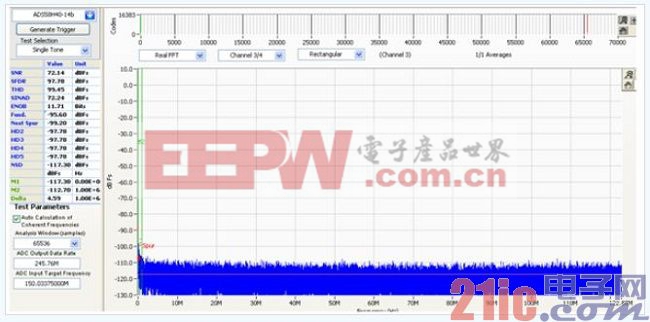

经过 PCB 布局优化的 ADS58H40 使能 DC offset correction function 后不再具有纹波底噪,而且 ADC 底噪更佳(Figure 8)。在-60dBFs 的小信号扫频测试中,去除模拟输入端滤波器的影响后其波动在 0.5dB 以内。

Figure8NormalnoisefloorafterPCBlayoutoptimization

5、结论

ADC 的 DC offset correction function 可以有效的抑制直流偏移所带来的误差。不过在PCB 布局不当时,开启此功能所带来的码域翻转干扰会使 ADC 具有纹波底噪并且其采集到的小信号幅度波动会达到 3dB 以上。通过针对性的 PCB 布局优化可以有效的解决这个问题,将-60dBFs的小信号波动控制在 0.5dB 以内。

评论