基于位线循环充电SRAM模式的自定时电路设计

HBLSA-SRAM不仅可以降低位线的电压摆幅,还可以有效地减小位线的电容负载。位线的负载电容很大程度上取决于位线上连接的MOS管数量。如图1所示,在每一个Group中有M个存储单元,而一共有N个Group,所以总共有M×N个存储单元。对于一个传统的SRAM结构有如此的容量,那么其位线上一共会接M×N个MOS管。但对于HBLSA-SRAM来说,将连接到主位线和局部位线的MOS管加在一起也不过N+M+5个。其中,对于主位线一共连接N个MOS管,而局部位线一共连接M+5个MOS管,M为M个存储单元的传输管,有1个来自与主位线连接的MOS管,另外4个来自局部的灵敏放大器。所以,不但位线摆幅显著下降,而且位线电容负载也下降了。

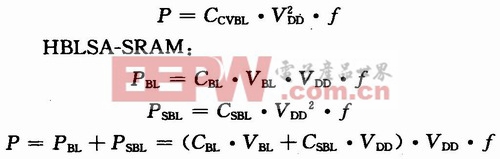

HBLSA-SRAM的读写功耗与传统的SRAM比较如下:

(1)对于写入功耗

传统的SRAM:

式中:PBL代表主位线上的功耗;PSBL代表局部位线上的功耗;CBL代表局部位线的电容负载;CSBL代表主位线的电容负载;CCVBL代表传统结构位线的电容负载;VBL代表局部位线的电压摆幅。通过之前的分析,有(CBL+CSBL)CCVBL,VBLVDD。所以,显然HBLSA-SRAM的写入功耗小于传统的SRAM。

(2)对于读出功耗

传统的SRAM:

式中:VCVBL代表读出传统结构的位线电压摆幅。可以认为,VCVBL和VBL近似相等,所以HBLSA-SRAM的读出功耗也小于传统的SRAM。

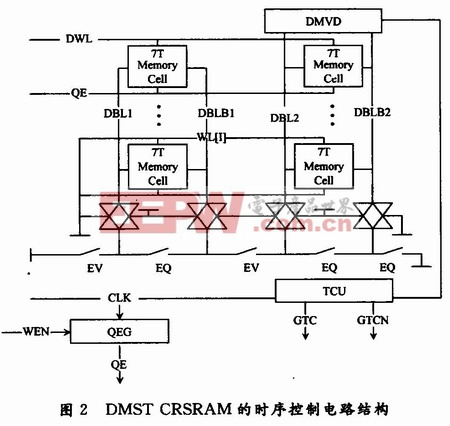

2 基于位线循环充电SRAM模式的自定时电路设计

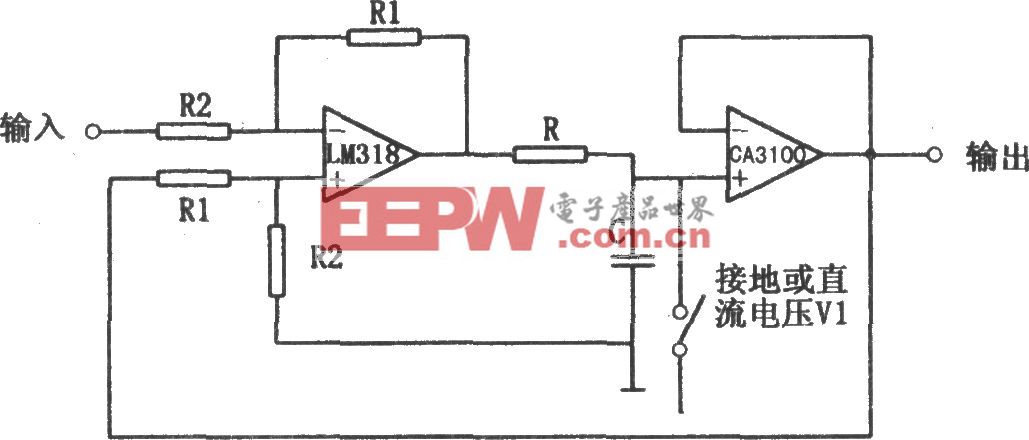

将位线循环充电SRAM的结构与双模式自定时电路相结合,为了进一步减小CRSRAM的功耗和优化器读写延时,提出基于位线循环充电SRAM的双模式自定时电路结构(DMST CRSRAM)。其时序控制电路如图2所示。本文引用地址:https://www.eepw.com.cn/article/180310.htm

评论