一种200V/100A VDMOS 器件开发

4 测试结果

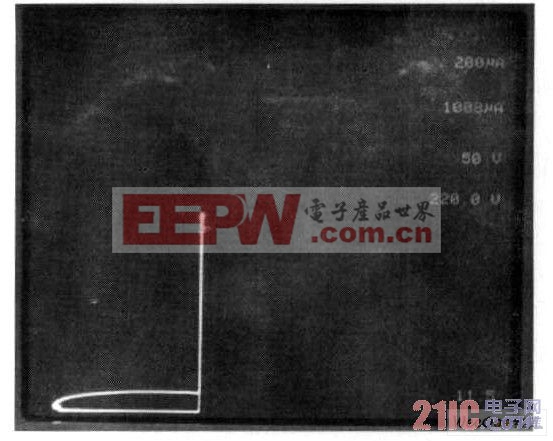

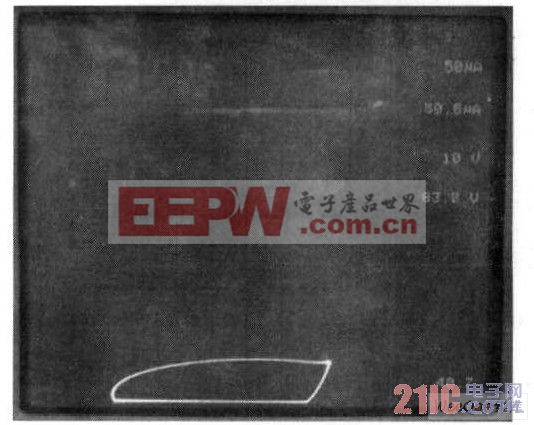

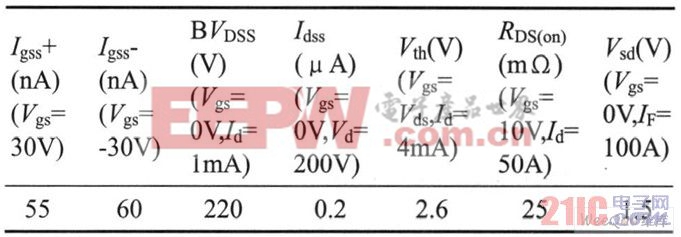

流水所得芯片如图5 所示,面积14400 μ m ×10800μm,其中左边两个角上深色方块为栅极压点,中间区域七个深色图形为源极压点。采用JU NODTS1000 系统测试结果如表2 所示,各参数良好,其中RDS(on)和Vsd 均为脉冲测试。图6 为元胞扫描电镜图片,其中N 阱、P 阱及多晶硅下的“鸟嘴”清晰可见,后者显着减小了该区域栅电容。图7、图8 分别为Tektronics 371 晶体管图示仪测试所得漏源击穿电压和栅源耐压波形,可见器件漏源击穿特性良好,栅源耐压大于83V,达到本征击穿。

图5 200V/100A芯片照片

图6 元胞扫描电镜分析

图7 漏源击穿电压波形

图8 栅源耐压波形

表2 200V/100A VDMOS器件参数测试结果

5 结论

本文采用圆弧形分布沟道与局域氧化相结合的方法开发出一种200V/100A VDMOS器件,在一定程度上解决了器件导通电阻改善与开关损耗增大的矛盾。对流水过程中的关键工艺进行了监控,所得器件具有较好的综合性能, 为国产大电流功率MOSFET 器件研发探索出一条途径。

评论