程控任意波形功率电源的研究

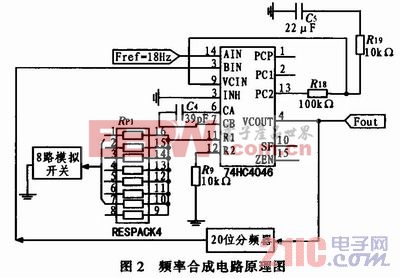

然后分别确定各个频段外接电容C1和R1、R2的参数,分段合成所需频率。最后控制系统根据不同的设置频率控制模拟开关接通相应的电子元件即可。频率合成部分的电路原理图如下图2所示,其中20 bits的分频器由FPGA实现。本文引用地址:https://www.eepw.com.cn/article/178879.htm

3.2 地址计数器和数据存储器电路

通过可变频率时钟控制地址计数器产生连续的地址以读取相应数据存储器内的波形数据,即可实现不同数字波形的生成。波形数据的深度为36,因此相位分辨率为360°÷36=10°。由于两路输出信号是相互独立的,在双路输出具有一定相位差的信号时需要经计算后分别改变地址计数器的初始预置数以进行输出波形初始相位的调节。

波形数据宽度为16 bits,数据深度为36,以存储10种波形数据计算,则共需36x10x2 Bytes=720 Bytes的存储空间。实际配置1 KBytes的存储空间,同时为了实现能够通过单片机写入数据而达到改变波形的目的,采用双口RAM比较方便。由于输出数据宽度为16 bits,因此只需9 bits的地址线即可,则地址计数器配置输出数据宽度为9 bits的计数器,同时计数器的预置数端用以预置初始值以改变输出波形的初始相位,该预置数经由锁存器锁存后输出至预置端。此外,由于单片机数据宽度为8 bits,故双口RAM的写入数据宽度配置为8 bits,其地址线宽度为10 bits,而输出数据宽度为16 bits。该部分电路全部由FPGA芯片配置而实现。

3.3 D/A转换及幅度调节电路

模拟波形重建采用DAC MAX5885芯片,其参考基准电源由DAC1210芯片控制以实现幅度调节的目的。

MAX5885先进的16位、200 Msps数模转换器(DAC),满足设计的要求。该DAC工作于3.3 V单电源,可提供无以伦比的动态性能,如77 dBc的无杂散动态范围(SFDR)(fout=10 MHz时)。该DAC支持200 Maps的更新速率,且功耗小于200 mW。

MAX5885采用电流导引结构,该结构支持满量程输出电流范围2~20 mA,允许差分电压输出摆幅在0.1 Vpp至1 Vpp之间。MAX5885具有集成的1.2 V带隙基准和控制放大器,以保证高精度和低噪声特性。此外,单独的基准输入允许用户外接基准,以获得最大的灵活性和提高增益精度。MAX5885的数字和时钟输入设计为CMOS兼容电平。

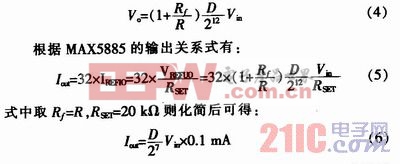

采用DAC1210实现数字控制模拟信号增益时,将其电路输出设计为:

其中D为数据宽度12 bits的数字量。这样,即可通过设置DAC1210的数字量来控制输出电流的大小,而另一路电压输出可以由电流-电压转电路实现。

评论