解析基于开关电源驱动的高速ADC设计方案

采用CMOS技术的ADC

当关注如何在保持较佳的SNR和SFDR性能的同时也尽可能地降低功耗时,我们一般利用CMOS技术来开发高速资料转换器。但是,CMOS转换器的PSRR一般并不如BiCOM ADC的好。ADS6148产品说明书列出了25dB的PSRR,而在类比输入电源轨上ADS5483的PSRR则为60dB。

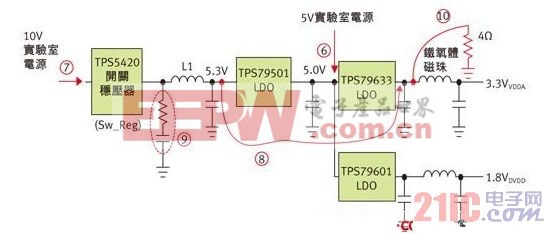

ADS6148EVM使用一种板上电源,其由一个交换式稳压器(TPS5420)和一个低杂讯、5V输出LDO(TPS79501)组成,后面是一些3.3V和1.8V电源轨的低杂讯LDO(请参见图10)。与使用ADS5483EVM的5个实验类似,我们使用ADS6148EVM进行了下面另外5个实验,其注意力只集中在3.3VVDDA电压轨的杂讯上面。1.8VDVDD电压轨外置TPS5420实验显示对SNR和SFDR性能没有什么大的影响。

图10:使用ADS6148EVM的5个实验电源结构。

实验6

将一个5V实验室电源连接到两个低杂讯LDO(一个使用3.3V输出,另一个使用1.8V输出)的输入。LDO并未对实验室电源带来任何有影响的杂讯。

实验7

将一个10V实验室电源连接到TPS5420降压稳压器,其与一个5.3V输出连接,像‘实验2’连接ADS5483一样。TPS79501产生了一个过滤后的5.0V电压轨,对于3.3V输出和1.8V输出LDO提供输入,如图10所示。

实验8

所有3.3VVDDA电压轨LDO均被加以旁路。TPS5420配置为一个3.3V输出,该输出直接连接到3.3VVDDA电压轨。TPS79601产生1.8VDVDD电压轨,并透过一个外部5V实验室电源供电。

实验9

该实验配置方法与‘实验8’相同,但去除了TPS5420输出的RC缓n器电路。

实验10

一个4Ω功率电阻连接到TPS5420的3.3V输出。这样做可大幅增加TPS5420的输出电流,因而类比一个附加负载。另外,像‘实验5’的ADS5483一样,它带来了更高的开关突波和更多的振铃。

图11显示了‘实验7’、‘实验8’和‘实验9’产生的一些3.3VVDDA 输出波形。有或无LDO的峰值电压振幅存在一些差异,但RC缓n器可降低60%的峰值杂讯。

图11:铁氧体磁珠后测得3.3VVDDA 电压轨实验示波器截图对比。

测量结果

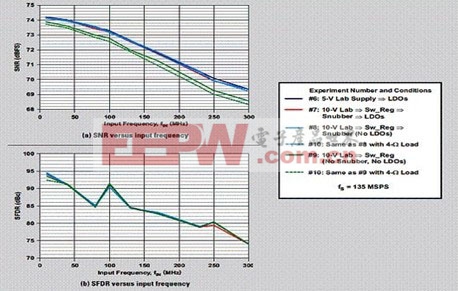

利用输入讯号频率扫描,透过比较‘实验6’到‘实验10’,我们可以研究ADS6148对电源杂讯的感应性。先使用135MSPS然后使用210MSPS的裱速率(fs)对叁个ADS6148EVM进行数次实验。我们并未探测到较大的性能差异。

使用135MSPS裱速率,SNR和SFDR的频率扫描如图12所示。高达300MHz输入频率下SNR的最大变化为0.1到0.2dB。但是,一旦移除了RC缓n器电路,杂讯便极大增加,因而降低SNR约0.5到1dB。

评论