宽带低相噪高分辨率频率合成器设计

主线圈驱动电路设计如图2所示,这部分电路是在锁相环路之外,有助于实现频率合成器的快速锁定,为精确调谐YTO主线圈,这里选用的是ADI公司的AD7528双8位DAC(D4),直接接受FPGA的并口数据控制(PRED0~PRED7),实现16位预置数送数的目的。AA0为低时送高8位预置数,AA0高为时送低8位预置数,运放TL072ACD完成了ADC的输出电流到电压的转换。经由R101、R102、R103和D6,其中R102=256R101组成的加法电路将两路电压相加。D/A送数改变MOS管IRF9520的G极、S极电压值,VGS电压差随着DA预置数增大而增大,VGS增大使D极电流ID变大,

MOS管IRF9520的D极直接与YT0主线圈相连,从而改变了流经YTO主线圈的电流值,达到调谐的目的。本文引用地址:https://www.eepw.com.cn/article/176843.htm

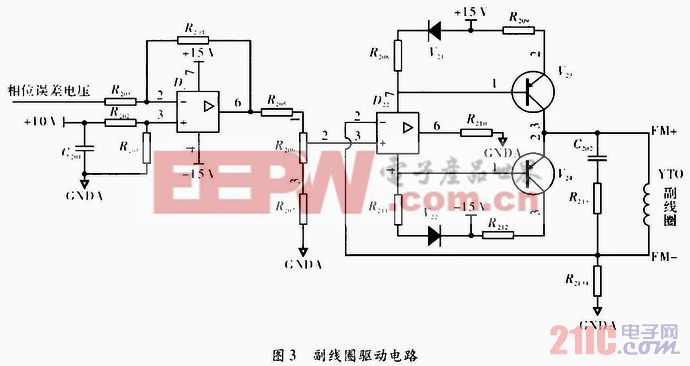

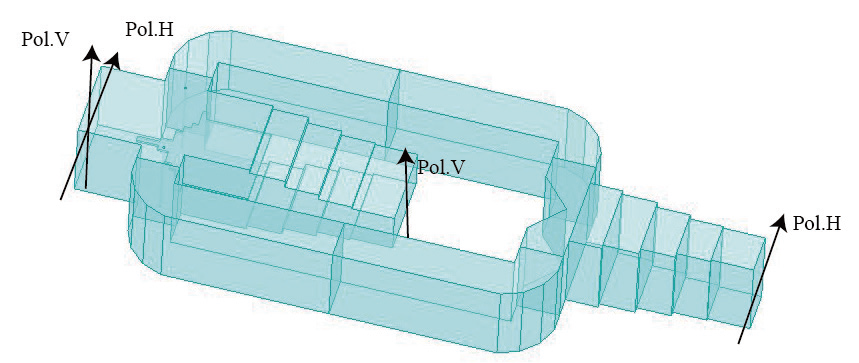

副线圈驱动电路设计如图3所示,为得到调频端合适的驱动电流和适应调频端的电流正、负偏,设计了一种驱动电路如图3所示。正的相位误差电压经带偏移的差分放大电路转变成正或负的电压,D22的3脚从变阻器R206的2脚获得相应的正或负的电压。文中使用的YTO调频端的调谐 灵敏度是300 kHz/mA,通过调节变阻器R206的2脚位置将环路捕捉带宽设定约为30 MHz。利用运算放大器D22两个电压输入脚的等电位特性来获得YTO调频线圈的驱动电流。当D22的3脚输入电压为正时,V23导通,电流从YTO的FM+端到FM-端。反之,当D22的3脚输入电压为负时,V24导通,电流从YTO的FM-端到FM+端。

2.2 小数分频电路设计

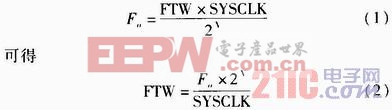

直接数字频率合成(DDS)作为新一代频率合成技术,具有输出频率分辨率高、频率切换速度快、相位变化连续以及数字可控等优点。采用小数分频在不降低鉴相频率的前提下,可以提高频率分辨率。本方案利用DDS芯片AD9858实现小数分频。AD9858内部集成有10位数模转换器,其频率分辨率为32位。根据公式

式中,FTW表示DDS频率控制字;F0表示DDS输出频率;N表示DDS频率控制字的位长;SYSCLK表示DDS参考时钟;YTO振荡器输出3~7 GHz的频率经8分频为375~875 MHz作为AD9858的参考时钟。方案要求AD9858输出频率F0始终为100 MHz,根据式(2)可以计算出频率控制字FTW,由FPGA通过并行送给AD9858。由AD9858分频输出100MHz频率经低通滤波器后与100 MHz参考频率fr进行鉴相。根据式(1)可以计算出频率分辨率为0.09~0.2Hz。

2.3 环路滤波器设计

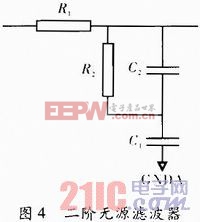

在锁相环路中,环路滤波器起着至关重要的作用,它将误差电流分量转化为误差电压分量,滤除误差电压中的高频分量和噪声,以保证环路所需要的性能,增加环路稳定性。在锁相环电路设计中,为达到优异的相位噪声,人们往往采用无源环路滤波器完成设计,设计时需要重点考虑带宽,相位裕度,滤波器结构、阶数、极点等参数。在本方案中由于相位误差电压在0~5 V之间,故选择无源滤波器,利用PLL DesignSimulation V4.0仿真软件设计出环路带宽200 kHz,相位裕度45°,阻尼系数0.707的二阶无源滤波器如图4所示。经实际调试后R1=2 kΩ,R2=39.2 Ω,C1=0.1μF,C2=11 nF。

评论