TMS320F2812与CPLD的视频采集系统接口设计

图像输入模块。图像的输入由模拟摄像头完成。摄像头输出的视频信号为标准的复合视频信号CVBS,必须经过视频解码芯片和A/D变换后进入数字系统才有效。模拟视频信号包含图像信号、行同步信号、场同步信号、像素时钟等信号。

图像存储模块。采用2片外部存储器SDRAMA和SDRAMB,用于存储数字视频信号,并将数据实时地传送给TMS320C6416进行数据处理。本系统采取两片存储器轮换读写的方式。

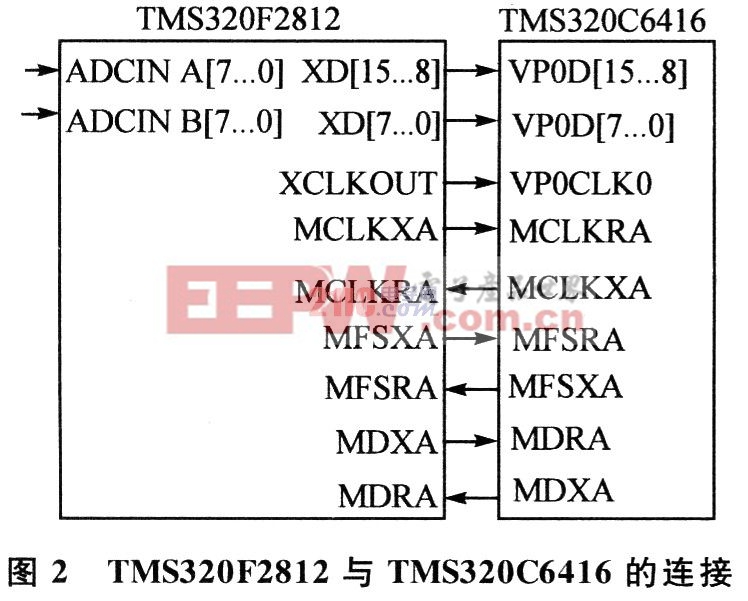

图像解码模块。负责将摄像头输出的模拟视频信号转换成Y:U:V=4:2:2的数字视频信号;并将图像逐帧存入SDRAM中,通过中断通知DSP读取数据。该图像解码模块采用的是TI公司的DSP芯片TMS320F2812。模拟信号经过处理后从TMS320F2812的系统外部接口XINTF的引脚XD[15…0]输出YUV422数字信号,YUV422信号输出到TMS320C6416的VP0端口,再通过多通道缓冲端口McBSP来控制TMS320F2812的工作。TMS320-F2812与TMS320C6416的连接如图2所示。本文引用地址:https://www.eepw.com.cn/article/173396.htm

CPLD控制模块。主要实现系统的逻辑控制和存储器地址译码功能。CPLD将经过同步分离后的行、场同步信号转换成YUV422格式的数字信号,同时产生SDRAM的地址、读写选通等信号。由CPLD输出的YUV422格式的数字信号按像素逐个存入2片存储器中,其中2片SDRAM以乒乓方式工作。这里CPLD选用Altera公司的EPM7128芯片。

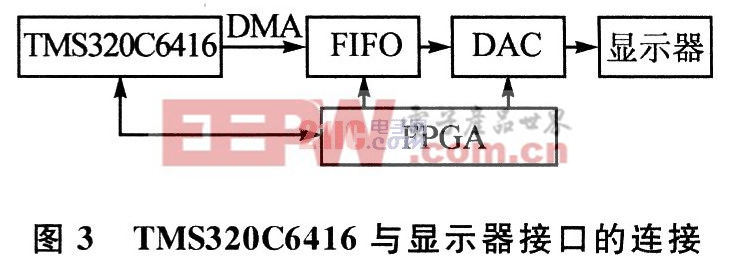

DSP图像处理与显示接口模块。选用TI公司的DSP芯片TMS320C6416。该芯片有HPI和EMIF接口,2个外部总线接口EMIF-A和EMIF-B的时钟为100MHz,2片存储器被映射到这2个总线上。其中,SDRAMA映射到EMIF-A,256 MB,64位宽,800 MB/s的瞬时突发率;SDRAMB映射到EMIF-B,8 MB,16位宽,200 MB/s的瞬时突发率。可以方便地与其他处理器连接,有实时的硬件调试功能。开发工具包含CCS环境、DSP BIOS、JTAG扫描控制器等。CPLD写完一帧图像后发中断信号通知DSP读取,DSP执行中断服务程序从SRAM中将一帧图像读入,随即进行处理。其模块与显示器接口的连接如图3所示。

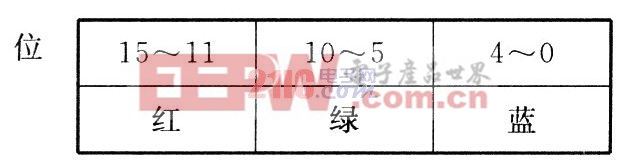

FPGA用于对FIFO的读/写时序与逻辑控制。FIFO的写时序信号由TMS320C6416的EMIF外部总线产生。通过DMA方式将视频数据写入FIFO缓存器中,再通过DAC输出视频编码器将YUV422格式的数字信号转换成SVGA格式的RGB信号格式,并将它输出到显示器上。输出VGA分辨率为800×600(SVGA制),但在TMS320C6416存储器中的像素格式为RGB565。每个像素存储在16位的存储器中,其SVGA输出像素格式的存储方式如下:

评论