数字网络视频监控器中多路转接逻辑的设计

输入格式转换模块主要是完成四路信号从d1到cif格式的转换,即从原来的720*576像素的分辨率转换为352*288像素的分辨率。其转换过程是把一帧中偶数行的数据全部去掉,每一行中按像素的顺序一个隔一个的去掉,最后保留的数据就是原来1/4的数据。这个过程比较简单,通过设计两个行列计数器就能实现。其仿真图如图5所示。

图5 d1到cif格式转换的简单仿真示意图

图5所示为在奇数行时数据一个空一个的有效,在一行读完后,下一行就都设为无效。

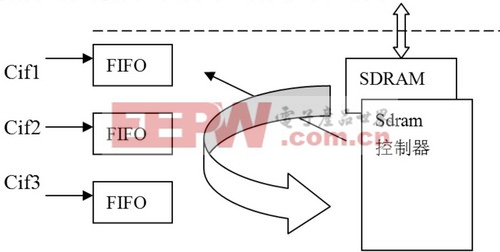

接下来是内部输入缓冲模块,此模块用来控制与SDRAM控制相连接和进行数据缓存控制的模块。其内部逻辑图如图6所示。

图6 FPGA内部缓冲与内部SDRAM控制器的连接逻辑图

下面给出对此次设计以后可以扩展和改进的功能。

首先,因为这是四路的多路转换缓冲,所以直接把它们固定组合起来送至网络显示终端。如果需要支持更多路的视频信号输入进行多路转换,例如输入信号是8路或16路,那么送入网络的时候就有一个组合的问题,即在显示器上四幅图像最终显示视频输入的哪四幅。这在实际情况下也是经常出现的情况,例如在某个建筑物中安装了8个摄像头,在白天的情况下可能要监视楼道内的情况,而到晚上可能要监视楼外门口的情况,这就需要在FPGA中进行一个选择,所以,此时可以在FPGA中加入一个I2C从模块,通过此模块可以与处理器通信,在FPGA中设置一些寄存器,通过由I2C送来的不同的寄存器配置指令,就可以实现显示器上图像的实时切换。

其次,由于Cyclone系列的产品存储容量比较有限,如果要增加到16路这样的规模,输入输出缓冲的存储容量必将不够,所以此时可以考虑用Cyclone2系列的产品。

另外,如果以后要完成路数比较多的转接,可以在监控器板上多加几块TW2804和VW2010芯片,这样就需要FPGA的输入输出引脚要足够多,而EP1C6Q240C8这样的FPGA芯片有240个引脚,足够扩展需要。

总之,在这样的转接逻辑中用到Altera的Cyclone系列低成本的FPGA产品,充分利用了其现有的内部资源,而且价格也是非常的易于接受,是非常理想的选择。

本次设计项目是作者年初在龙芯产业化研发中心作客座研究生时独立负责设计并实现的,其中此次视频监控器的CPU用的是龙芯2号,此转接逻辑已成功设计完成。

评论