数字网络视频监控器中多路转接逻辑的设计

如图1所示,A/D芯片接受来自四个摄像头的四路模拟视频信号,这里采用Techwell公司的TW2804芯片,此芯片支持四路视频模拟信号的输入,输出是数字ITU-R BT.656格式的信号,时钟是27MHz。D1、D2、D3、D4信号的时序图如图2所示。

图2 ITU-R BT.656格式信号时序图

其中EAV和SAV分别为行尾和行头标志信号,他们中间是行与行之间的空白信号,SAV后面的VALID有效时的信号为1440bytes的d1格式的有效视频信号,总的这些信号加起来是视频信号的一行信号,一帧视频信号包括576行这样的行信号,也就是有效的这种格式的一帧输出视频信号为1440*576bytes的信号,由于每一行信号中由两个bytes来表示一个像素,所以这种d1格式一帧的像素为720*576分辨率。

FPGA转接逻辑要实现的功能是要在显示终端上同时显示四路的视频信号。也就是要显示如图3所示的视频信号。

由于要在一个显示终端上同时显示四路信号,所以原来每一路信号的720*576分辨率要转换为原来1/4的分辨率,即cif的格式,cif格式是352*288的分辨率,这样四路cif格式的信号组合成如图3所示的一个帧输出到终端显示出来。

因为在终端显示上是要求四路视频信号同步输出的,也就是不允许出现其中一路信号已经在显示器上显示出来了,但另外一路信号还没有显示出来,也就是出现画面上一部分是黑屏的情况,所以在这种情况下,需要把四路不同的视频信号先用FPGA在SDRAM中缓存起来,当每一路信号都在SDRAM中都至少存满一帧时就可以同步读出,并通过FPGA内部缓存组成如图3所示的帧格式,然后输出给压缩芯片压缩后由处理器控制输出至网络,这里的压缩芯片选的是VWEB公司的VW2010。

图3 显示终端视频信号格式

至此,FPGA要实现的功能已经非常清晰,首先把输入的四路d1格式的信号分别转换成四路cif格式的信号,然后把这四路信号分别缓存在SDRAM中,当SDRAM中每一路信号都至少存满一帧时,同步读出,读出SDRAM到FPGA中后,经过格式的重新组合,最后组成如图3所示的信号格式输出。其中数据在SDRAM中的缓存控制是最重要也是最复杂的环节。下面详细介绍此FPGA的逻辑设计与实现。

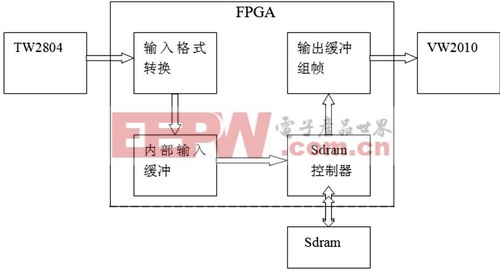

由上面的介绍可知,此FPGA主要有三方面的接口,与TW2804的输入接口,与SDRAM的缓存接口,与VW2010的输出接口。所以FPGA的内部逻辑大致可以设计为如图4所示。

图4 FPGA内部逻辑结构框图

评论