ADS8344与TMS320LC545的应用接口设计

2.2 ADS8344的引脚排列及说明

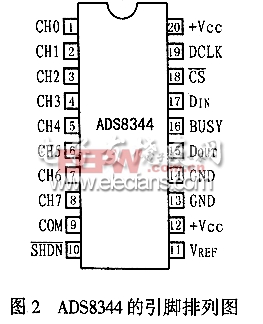

ADS8344的引脚排列如图2所示,各引脚说明如下:

CH0~CH7:模拟输入通道的输入端,8个单端模拟输入通道可合用为双端差分输入,所有通道的输入范围从0V到+VREF,未用的输入通道应接GND以避免噪声输入。

COM:模拟输入的参考地,单端输入通道的零地位点,直接接地或接地电位参考点。

SHDN:掉电控制位,当为低时,芯片切换到低功耗掉电模式。

+VCC:电源输入端,范围为+2.7V~+5V。

DOUT:串行数据输出端,在DCLK的下降沿时数据输出,当CS为高时,输出为高阻态。

DIN:串行数据输入端,当CS为低时,数据在DCLK的上升沿被锁存。

DCLK:外部时钟输入端,该外部时钟决定了芯片的转换率(fDCLK=24fSAMPLE)。

CS:片选端,为低电平时,选中该芯片。

GND:参考地。

VREF:参考电源输入端。

BUSY:模数转换状态输出引脚。当进行模数转换时,该引脚输出低电平,当BUSY端产生一下降沿时,表示模数转换结束,数据输出有效。

评论