基于可编程芯片的软件无线电试验平台的设计

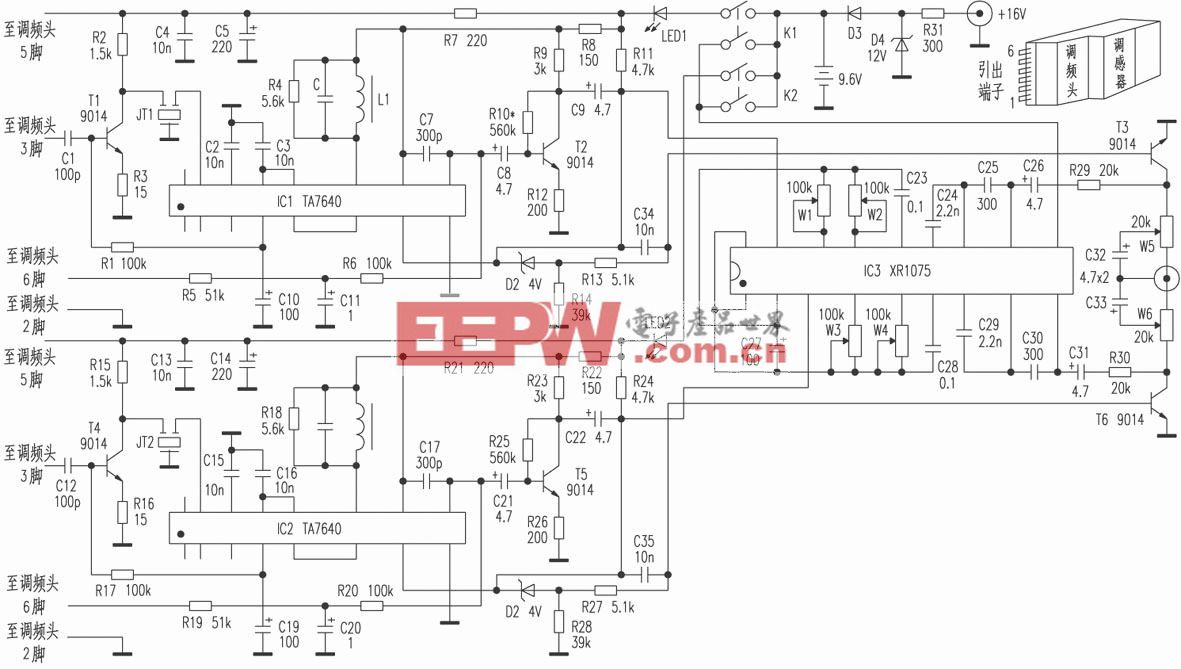

系统的硬件结构主要包括总线控制器S5933、外部FIFO、全局控制器CPLD、数字上变频器件HSP50215、数字下变频器件HSP50214B、HSP50210、高速D/A器件AD9762等单元。如图3所示,待发射的基带信号由PCI总线输入,经FIFO缓存后送入数字上变频器件HSP50215输出的数字信号转化为模拟中频信号;高速和A/D器件将中频的调制信号数字化后传输给HSP50214B,下变频得到的基带信号经FIFO缓存,由S5933经PCI总线传给计算机处理。

2 各个功能模块分析

2.1 总线控制器S5933

S5933是由AMCC公司生产的一种功能强、使用灵活的PCI总线控制器专用芯片,该

芯片符合PCI局部线规范2.1版。它提供了操作简单而功能强大的开发接口:PCI接口与Addon接口,PCI接口与PCI部相连,Addon接口与用户的电路相连,用户不用理会PCI总线的繁琐规范,只需对Addon接口进行PCI扩展板的设计。S5933支持DMA传输,它的峰值传送速率为132MB/s(32位PCI数据线),完全可以满足基带信号的双向传输。

S5933提供3种数据伟输方式:信箱方式、PASSTHRU方式、FIFO方式。信箱方用于PCI总线与Addon

接口之间进行简单的数据传输。PASSTHUR方式使得主机以访问内存的方式访问Addon接口的扩展空间。FIFO方式可以实现数据在PCI总线上进行DMA传输。此我们利用PASSTHRU方式实现对扩展板和可编程芯片的控制字和滤器系数的访问,使得此试验平台可以工作在不同的方式中。利用FIFO方式实现基带信号在PCI总线上的DMA传输。

2.2 可编程字下变频器HSP50214B一HSP50210

HSP50214B是由HARRIS公司生产的一种可编程数字下变频芯片,它对数字化中频信号进行下变频、抽取滤波、窄带低通滤波、增益控制、重采样、坐标转换的数字信号处理,输出的基带信号可以由一般的DSP或通用微机处理。HSP50214B支持各种数字解调方式(如BPSK、BASK、MPSK、MSK、MQAMD等)和各种模拟解调方式(如AM、FM、VBS、SSB等)。输入的数字化中频信号的速率可达65MSPS,输出的基带信号和速率可达12.94MSPS,带宽可达982kHz。它是的一个重要特必是可以通过改变内部寄存器的值从而改整个芯片的工作方工和状态,我们可以通过软件改变解调的方式、中频信号的输入方式、载波的中心频率与相移、数控振荡器的频率、增益控制的方式、输入和输出数据的格式等;另外,HSPO50214B中有两个(I、Q两路通道)可编程的256阶滤波器,它具有整形和抽取的功能。

HSP50210是由HARRIS公司生产的一种数字载波相位估计器件,它与HSP50215一起完成PSK信号的解凋。

2.3 可编程的数字上变频器HSP50215

HSP50215是上HARRIS公司生产后种编程数字上变频芯片,它支持各种数字调制方式(如BPSK、MPSK、MSK、MQAMD等)和各种模拟调制方式(如AM

、FM 、VBS、SSB等)。HSP50215的基带数据的输入率可达3.23MSPS,而经它上变频调制的信号的输出率呆达52MSPS,输出的中频载波频率在10-20MHz之间。它是一个重要特性是可以通过改变内部寄存器的值从而改变整个芯片的工作方式和状态,我们可以通地软件改变调制的方式、基带信号的输入速率、载波的中心频率、输入和输出数据的格式、同步方式等;另外HSP50215中有两个(I、Q两路通道)可编程的256阶滤波器,它具有整形和插值的功能。

2.4 全局控制器CPLD

整个系统的所有控制逻辑由一片CPLD器件(Altera公司的的EPM7192)承担,其控制对象包括S5933的Addon接口、外部FIFO、HSP50215的控制接口HSP50214B的控制接口。全避控制器主要完成以下任务:设置HSP50215内部寄存器;实现基带数据主机内存与HSP50215输入通道之间的传输以及实现基带数据主机内存与HSP50214B输入通道之间的传输。对于下变模块,由于解调的过程存在相位和载波同步的问题(由HSP50210完成),所以在系统的工作过程中要在线改变HSP50214B内部寄存器,设计控制逻辑中要着重考虑。对于变频模块,由于调制过程中不存在类似于锁相环的反馈结构,这意味着一旦启动基带数据传输后不需要更改HSP50215控制参数。因此写HSP50215控制字与基带数据传输是两个相互独立的控制逻辑,这使得设计过程比较清晰。

评论