L波段直接数字式快跳频率合成器设计

(3)去耦

减小来自电源的噪声。在同一块PCB中,通常多个器件共用一个电源。而电源线给交流信号提供了一个通路,使得交流信号通过电源线在器件之间传输,形成了干扰。所以必须在器件之间的电源线上加入滤波部分,滤掉交流干扰,称为去耦。在本设计中走线时尽量加粗了电源线宽度,减小环路电阻并在电源引入印制板处加了大容量的电解电容和小容量的高频电容,用于分别滤去低频噪声以及高频噪声。并且在每个集成电路电源引脚处增加0.1的高频去耦电容,加强去耦并提供和吸收该集成电路开关门瞬间的充放电能。本文引用地址:https://www.eepw.com.cn/article/154532.htm

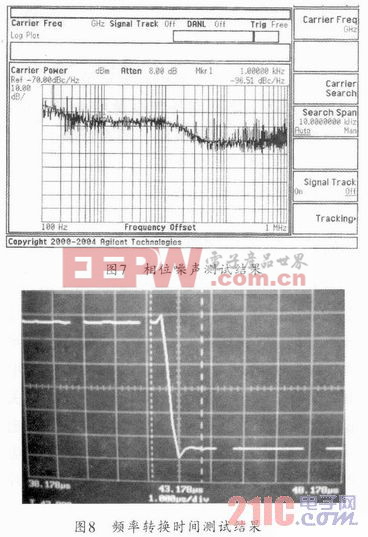

经过测试,快跳频率合成器相位噪声如图7所示,频率转换时间如图8所示。

4 结束语

本文中快跳频率合成器采用DDS激励倍频链的频率合成方式,用倍频的办法将频率搬移到所需频率波段上。在实际应用中,通过不断的实验和改进,该快跳频率合成的工作频率范围、频率准确度及稳定度、频率转换时间、相位噪声、杂散电平都可以满足技术指标要求。

评论