高速DSP串行外设接口设计

4.1寄存器整体电路设计

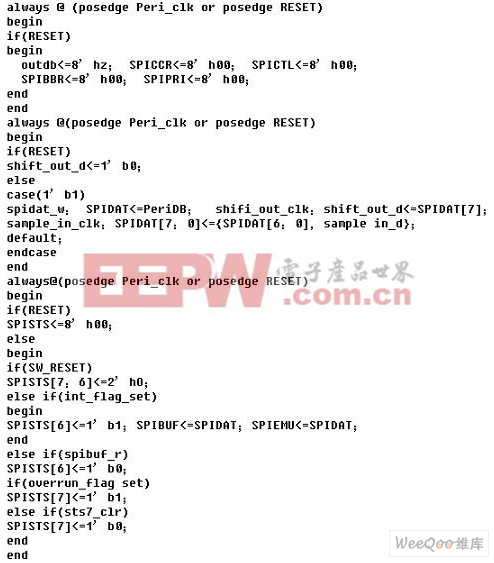

下面是部分Verilog HDL源代码.描述了数据传输时相关寄存器的功能设置:先是对复位时各个寄存器的初始值,接下来是对寄存器进行功能设计.和数据传输时候产生的中断使能和标志位的设计。

4.2整体时序仿真

将上述Verilog代码编译,再写上对应测试代码进行验证。图5是寄存器的写操作的整体时序仿真波形图.验证了上述代码正确可行。

图5写操作整体时序仿真

5 结论

本文作者的创新点是改进了硬件触发器的结构.用三态门和传输门取代那种单一MOS管的结构。首次应用到TMS320LF2407芯片串行外设接口上,降低工作电压到3.3V,加快数据传输,而且还有相应的反馈信号,进一步完善了触发器结构。同时有很好的可移植性好。具有充分的可裁剪性,本设计运行可靠,达到预期的效果。

评论