逻辑分析仪SignalTaPⅡ在系统级调试中的应用

在SignalTap II的采样之前,要进行相关设置,比如要观察产生的正弦波,先将拨码开关12(sel[1..O])设置为“00”(三角波时设置为“01”,方波是设置为“10”),再将拨码开关3(rst)由0变为1,产生一个上升沿,作为SignalTap II的采样触发信号。这时执行Autorun

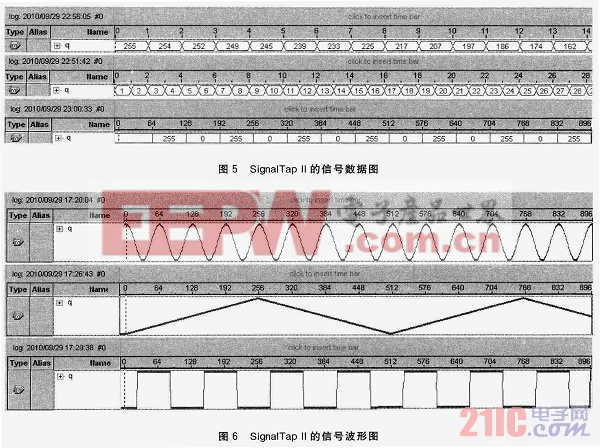

Analysis,就能在SignalTapII数据窗观察到来自实验板上FPGA内部的实时信号,如图5所示。图中依次为正弦波、三角波和方波数据。数据窗的上沿坐标是采样深度的二进制位数,全程是1024位。

为了更直观地看到波形图,不需要进行数/模转换,直接右键单击所要观察的总线信号名,在弹出的下拉菜单中选择总线显示模式“Bus Display Format”为“Line Chart”,即可获得如图6所示的模拟信号波形。

从图5、图6可以看出输出结果和设计需求是一致的,验证了设计的正确性。如果采用传统的硬件测试方法,在本系统中还需要加入D/A转换模块,利用示波器观察波形。故利用SignalTap II进行系统的硬件测试是非常方便的,可以加快系统的开发流程。而在整个工作流程中,STP文件的参数设置是至关重要的,它直接影响测试结果。例如在本系统中,采样时钟采用分频后的信号,而不是采用主时钟,因为主时钟频率太高,不便于观察输出信号。另外还有触发信号的选择,启动采样前开关的设置,都会直接影响输出信号。

4 结论

嵌入式逻辑分析器SignalTap II克服了传统硬件测试的缺点,为系统测试提供了一个很好的途径。它具有实时性和可视性,减少了调试验证的时间,加快了设计周期。通过对Cyclone II系列EP2C8Q208C8器件的实验,证实该测试手段提高了系统的调试能力,具有很好的效果。在调试FPGA的时候,可以设置多个嵌入式测量模块等其他功能,这样可以加快系统的开发,为社会带来更大的经济效益。但是它需要占据FPGA资源(如RAM、LE等),且资源消耗量与需采集的数据量成正比,因此采集信号的深度不能过大。此外,当利用SignalT印II将芯片中的信号全部测试结束后,需将SignalTap II从设计中移除,以免浪费资源。

评论