基于NiosⅡ的电能质量监测系统设计

2.2 NiosⅡ软核处理器

本文引用地址:https://www.eepw.com.cn/article/150259.htm基于32位RISC嵌入式软核NiosⅡ的SoPC,有着其他SoPC(如基于FPGA嵌入式IP硬核SoPC)不可比拟的优势。采用NiosⅡ软核处理器,用户将不会局限于一般的处理器技术而是根据自己的标准裁剪和定制处理器,按照需要选择合适的外设、存储器和接口,轻松集成自己专有的功能,比如DSP、用户逻辑等。这非常有利于设计高次谐波这种计算量大且控制逻辑复杂的系统。

为了满足今后的性能要求,该电能质量监测系统应能随时被改进升级。可以加入多个NiosⅡCPU、定制指令集、硬件加速器等,以达到更好的性能目标。还可以通过Avalon交换架构调整系统性能,该架构支持多种并行数据通道可实现大吞吐量的应用。

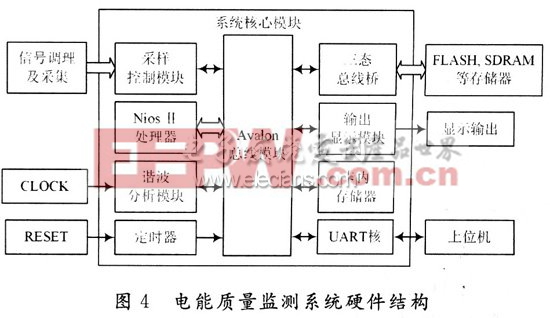

2.3 硬件系统平台设计

图4是整个系统的硬件结构框图。系统组成主要包括:

(1)系统核心模块采用STRATIX系列的EPlS25型的FPGA,它包含:10个DSP模块、25 660个逻辑单元、48个嵌入式乘法器、RAM总量高达1 922 576 b,6个数字锁相环、可用的I/O口最多达到702个。它是一款采用高性能结构体系的PLD器件,结合了强大内核性能,大存储器,DSP功能,高速I/O和模块化设计。其内嵌的DSP模块,提供了高于DSP处理器的数据处理能力,可以完成较为耗费资源的乘法器单元。这些资源对一个电能质量监测系统来说是已经绰绰有余。

(2)NiosⅡ软核处理器是整个系统模块的CPU,它的具体特性已在前面详细叙述。NiosⅡ软核处理器除了要协调控制各个硬件设备外,电能参数相关数据的软件算法也要在此执行。

(3)Avalon交换式总线由SoPC Buiider自动生成,它是一种用于系统CPU和外设之间的内联总线。传统的总线结构缺点是每次只能有一个主机能接入总线,导致带宽瓶颈。而在Avalon总线结构里,总线主机不抢占总线本身。Avalon交换结构可实现数据在外设与性能最佳数据通道之间的无缝传输,并且它同样支持用户设计的片外处理器和外设。

(4)谐波分析模块采用内嵌的DSP对采集过来的16位数字信号进行处理,输入电能计量指标参数的处理算法程序,将结果暂存在片内存储器,最后NiosⅡ软核控制单元通过RS 232或.RS 485串口完成数据的传输和人机对话。谐波是一个周期性的正弦波分量,其频率为基波频率的整数倍。进行谐波变换的方法很多,本文采用的是FFT,完成电压有效值、电流有效值、有功功率、无功功率、视在功率、频率、功率因子和稳态谐波分量等检测。

以上是本文提出的一个基于NiosⅡ的基本电能质量监测系统的硬件平台。根据不同要求,还可以采取往系统核心模块里添加DMA、自定义模块等措施,从而形成功能更加完善的电能质量监测系统。

3 电能质量检测系统软件设计

3.1 SoPC Builder设计

对应系统的硬件平台结构,添加NiosⅡProcessor,选择其为快速型,以确保系统的速度性能。再添加SPI,PIO,Character LCD,FLASH Memory,Avalon Tristate Bridge,SDRAM Controller,On chip Memory,DSP,timer这些模块。设置好模块的各项参数后,点击System控件里的两个选项为各模块主动分配地址和中断。然后在NiosⅡMore“CPU”Setting里选Reset Address为FLASH,选Exception AddFess为SDR-AM。最后点击Generate生成对应的ptf文件。这样系统的SoPC Bui[der设计基本完成。

3.2 NiosⅡIDE设计

进入NiosⅡIDE后新建一个应用工程,选择ptf文件和Black Project,这样一个基于已有SoPC的空白应用工程建立完毕。然后在System Library里进行必要工程设置。接着将电能参数算法的C程序填入工程里,再进行软件的编译调试等。调试完毕后,一并将所有程序与可执行文件全下载到FPGA上。至此,一个基于NiosⅡ的电能质量监测SoPC设计完成。

评论