基于TMS320F2808 DSP最小系统设计及应用

3.2 JTAG接口电路设计

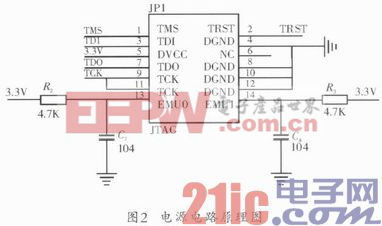

TMS320F2808采用符合IEEE 1149.1的JTAG仿真接口,仿真电缆和DSP芯片的JTAG仿真接口是通过一个14脚的双排插头/插座来连接的。扫描仿真消除了传统电路仿真存在的电缆过长引起的信号失真及仿真插头的可靠性差等问题。采用扫描仿真,使得在线仿真成为可能,给调试带来方便。考虑到JTAC下载口的抗干扰性,在与DSP连接的EMU0、EMU1端口必须通过4.7kΩ的上拉电阻连接至电源,/TRST引脚通过2.2 kΩ的下拉电阻接地,且分别在其引脚上添加0.1μF的旁路电容。JTAG接口电路连接如图2所示。本文引用地址:https://www.eepw.com.cn/article/148076.htm

3.3 引导加载模式选择

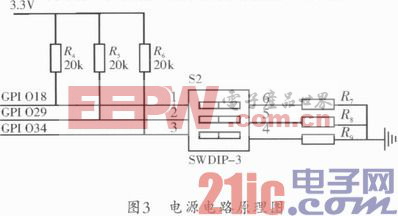

在进行硬件产品和系统设计时,用户程序通常保存在非遗失的存储器中。这些非遗失存储器的访问速度较慢,一般不能直接作为程序存储器来使用,需要在上电时引导到CPU的高速程序存储器中,这个过程称为BOOTLOADER。在TMS320F2808内部配置了一个引导ROOM(BootROOM)该ROOM内固化了一个引导加载程序、CPU向量表和一些数学表和函数。Boot ROOM大小为4 kB,占用地址空间为0x3F F000~0x3F FFFF。加载模式选择如表1。

通过设置GPIO引脚的状态即可确定选用哪种引导模式。引导模式电路如图3所示。

评论