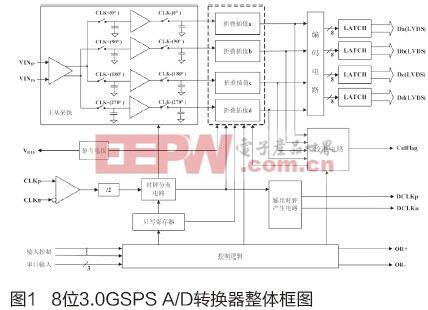

无采样保持运放的12位流水线A/D转换器

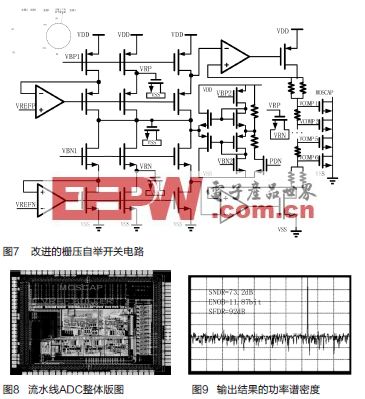

片上参考Buffer

参考电平产生主要有两方面应用,VRP、VRN用于对MDAC放大相的采样电容进行快速充放电,VCOMP1至VCOMP6给子ADC中的比较器提高比较参考电平。对于大的电容负载,要达到足够快的建立速度,要求VRP、VRN 的驱动电路具有很大的带宽,需要消耗大量的功耗。因此通常情况下更偏向于将参考电平拉到片外,通过外接大的解耦电容来稳定该电平。但是,这样不仅增加了引脚数量,同时外加器件增加了系统成本。本文设计的片上参考驱动如图7所示,VREFP和VREFN由Bandgap电路提供,由于支路2、3是支路1的镜像,因此VRP、VRN和VRP1、VRN1能够跟踪电平VREFP和VREFN。其中支路2要求有大的带宽来保证建立速度,因此支路2电流很大,为25mA。支路1,3没有建立速度要求不需要消耗太多功耗,电流为1mA。此外,电流平衡电路能够调节支路上下电流偏差,使管子工作在正常状态,保证了电路的稳定性。

版图与仿真结果

整体电路版图如图8 所示, 总面积为 2mm×2mm。仿真的OTA共模电平为0.6 V, 正、负参考电压为0.9 V 和 0.3 V, 输入信号为单频70MHz 正弦信号。仿真得到的整个电路的电流耗散为350mA 。ADC 整体电路的仿真结果如图9 所示。由于仿真时间的限制, FFT的点数只取951点。

由图9 的功率谱可以看出, 整个电路的噪底在100dB 附近, SFDR 为92 dB, 满足12 位ADC 的动态范围要求。由于采用全差分的电路结构, 整个电路基本没有二次谐波; 同时, 由于采用高增益运放和自举采样开关, 系统的奇次谐波, 尤其是三次谐波, 接近噪底。

结论

设计一个12 位200MHz 无采样保持运放的流水线ADC,采用SHA-less采样匹配网络,DLL时钟方案,保证中频采样动态特性;增益自举两级密勒补偿OTA提供了高增益和良好的建立特性,同时片上参考驱动电路避免外接电容,降低了系统成本。后仿真结果显示: 在输入信号为70MHz 单频信号时, 整个转换器能够达到92dB 的SFDR 和73.2 dB 的SNDR, 功耗为350mW。

比较器相关文章:比较器工作原理

锁相环相关文章:锁相环原理

评论