无采样保持运放的12位流水线A/D转换器

延迟锁相环时钟方案

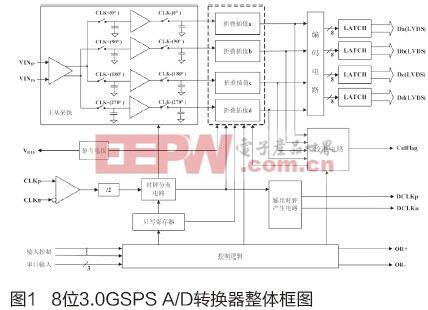

本文引用地址:https://www.eepw.com.cn/article/119876.htm由于流水线ADC的各级级电路工作在交替变化的两相不交叠时钟下,为了保证每级都能拥有平均的时间来工作,提供50%占空比的输入时钟非常重要。此外,从数据转换器的角度来看,随机的时钟抖动会在模数转换器何时对输入信号进行采样方面产生不确定性。因此要保证高速、高精度A/D转换器的性能,必须首先保证采样编码时钟具有合适的占空比和很小的抖动 。本文提出一种用于高速流水线ADC的时钟方案,该方案以延迟锁相环(DLL)电路为核心,由时钟输入电路,50%占空比稳定电路和无交叠时钟电路构成。对高频输入信号的采样时钟进行了特殊处理,能够有效减小时钟抖动。占空比稳定调节电路能够保证运放建立相脉宽从而使得运算能够建立完全。

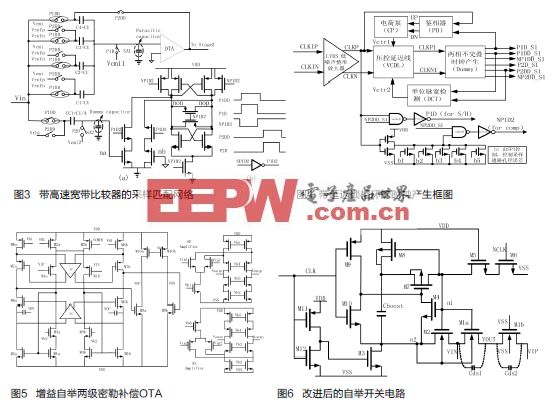

如图4所示,低压差分时钟输入信号CLKIP及CLKIN经过低噪声LVDS整形电路后转变为差分数字脉宽信号CLKP和CLKN。CLKP及CLKN经过8级延迟线单元的延迟后生成时钟CLKP1及CLKN1。CLKP1、CLKN1作为两相不交叠时钟dummy模块的输入,产生与第一级级电路同步的不交叠时钟信号作为延迟锁相环的反馈信号。一般来说,一个逻辑门将会产生几个皮秒甚至十几皮秒的定时抖动,因此为了减小时钟抖动,输入信号采样时钟应经过了尽可能少的逻辑门,图中CLKP经过少量逻辑门电路后直接得到第一级级电路MDAC底板采样时钟信号P1D和子ADC比较器锁存时钟信号NP1D2。鉴相器检测CLKP和P1D_S1的下降沿后生成的电荷泵充放电信号经过低通滤波后得到延迟单元延迟控制信号Vctr1。同时P1DD_S1和P2DD_S1信号经过单位脉宽检测电路后得到延迟线单元脉宽调节信号Vctr2。此外,采样网络时钟匹配通过由SPI接口输入的信号bi(i=1,⋯,5)控制NMOS阵列的开启数调节子ADC锁存器时钟下降沿来实现。其它各级级电路工作时钟信号由延迟锁相环延迟线输出CLKP1、CLKN1经过内部各自的两相不交叠时钟电路后生成,减少了全局时钟线数目,有利于版图设计。

电路设计

增益自举两级密勒补偿OTA

在200MHz 的采样速度下,要达到12 位精度,要求第一级运放增益大于100dB,12dB闭环增益带宽大于1GHz,输出摆幅大于0.6V。在低电源电压下,为了达到高的开环增益和大的输出摆幅,设计了如图5所示的密勒补偿两级OTA。其中,第一级为了实现高增益,采用了对称式cascode增益自举结构;第二级要达到大的输出摆幅,选择了简单的单管输出级电路。密勒补偿将电容反馈端接至cascode管的源极,可以将零点推至足够高频处而避免了对运放建立的影响,同时避免了去零点电阻的使用。共模反馈通过简单的开关电容共模反馈来实现。

开关

对于中频采样ADC,开关特性的好坏严重影响了整体转换性能,其非理想特性主要有有限导通电阻、导通电阻的非线性、时钟馈通效应、电荷注入及寄生电容耦合等。导通电阻阻值过大,使得采样RC带宽过小,严重限制了输入信号带宽和频率。随输入信号变化的电阻阻值及寄生电容都将恶化转换器的AC特性,降低线性度。为了尽量减小以上非理想效应,采用了图6所示的自举开关结构。首先将导通管M1a的衬底接至n2节点,可以去除衬偏效应的影响;其次添加与M1a同样尺寸的M1b虚拟管,可以消除高频输入信号通过漏源电容对采样电容输入端的耦合效应。

比较器相关文章:比较器工作原理

锁相环相关文章:锁相环原理

评论