运算放大器:单通道,双通道抑或四通道(上)

输入级电路

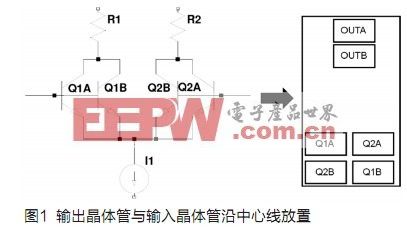

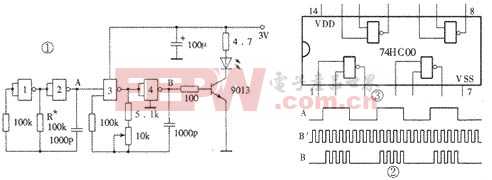

本文引用地址:https://www.eepw.com.cn/article/110159.htm运放的第一级通常是差分对电路,可以是如图所示的NPN或PNP双极性电路,也可以是N沟道或P沟道MOSFET,或N沟道或P沟道JFET。它们面临一个同样的问题:如果两边的温度有差异,即使相差只有1/10,电路也会变得不平衡。当增益为10万倍或以上时,这将对输出电压造成影响。当输出级电路存在功耗时,热波将越过裸片传播到输入级。如果输入级离得比较远(相对而言),等温线将近似平行线。如果两个输入晶体管的位置摆放得比较合适,热波将同时到达两个晶体管,这时平衡几乎不会受到影响。这是一个好主意,但我们可以做得更好。将晶体管分成两个部分,并进行交叉耦合,那么从某个角度传来的热波将同时影响两个部分,影响程度将低于两个独立晶体管的情形。也许George Erdi在 uA725中首次应用的就是这种方法[5]。“交叉耦合四通道”具有多方面的含义,这里讨论的是其最通用的含义。输出晶体管和输入晶体管应沿着图1所示的中心线放置。

版图设计还有许多其它考虑因素,如裸片应力、电阻的温度系数等,这些因素在Hastings的文章[6]中有很详细的介绍。

封装引脚输出

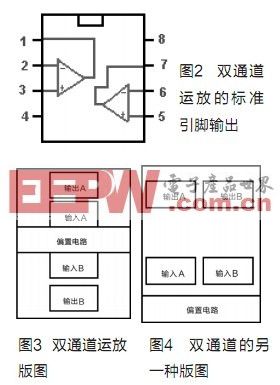

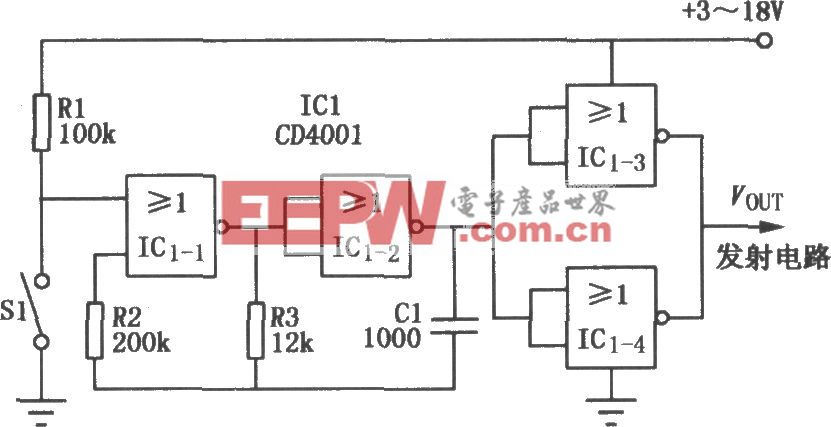

图1中的版图对单通道运放来说完全没有问题,但对双通道运放来说问题就出现了。双通道运放的标准引脚输出如图2所示。

图3是双通道运放在晶体管级的一种可能的底层规划图。这里有个问题:通道B的输出必须越过输入线才能到达引脚7。在很早以前,双极性模拟工艺还是采用的单层金属化工艺,必须使用穿接(cross-under)方法,因此对性能会有影响。

图3是一个很好的双通道运放版图。输入级非常靠近裸片中心,因此机械应力梯度最小。从一个输出级到另一个输入级的距离要大于另一种版图。从输出级到两个输入级的等温线近似等距的并行线,因此交叉耦合输入级四通道运放的抑制能力很强。这种版图的主要缺点是,输出B必须跨越两个输入级才能到达输出焊盘。从输出金属化到同相输入金属化的任何电容都将导致正反馈。这对几年前的单层金属化(SLM)工艺来说问题比较麻烦,不过通过这些运放的低增益带宽已经有所改善。这种版图具有良好的散热性能,但是,在规划同一产品系列中的四通道版本时又会遇到问题。 双通道版图还有另外一种选择,如图4。

绝对值编码器相关文章:绝对值编码器原理

评论