Achronix:22nm设计没那么烧钱,掩膜成本被高估

最近,Achronix 22nm称已经能提供FPGA样片,预计2季度末、3季度初会量产。Achornix的卖点是相对28nm同类产品,功耗减半、成本减半、设计时间减半[1]。

为何22nm后成本会减半?因为22nm时不仅制造费用高昂,设计费用也令人咂舌。另外为何设计时间减半?Achronix又进一步解释了他们的产品。

问:成本一半,是否有具体的比较数字,例如和其他FPGA厂商的产品的比较数字?为何成本会降低这么多?主要是从die面积减少测算出来的吗?因为22nm设计和掩膜的成本是很高的,只有达到足够的批量,例如几千万片以上,才能保证收支平衡。而Anchronix刚刚起步,面对高端市场,如何定价?

答:Achronix在其FPGA中集成了高带宽和连接通信技术硬核IP。使用硬核IP的客户将可以节省一部分FPGA资源,否则该部分资源必须用来实现通信协议功能。这意味着在用以实现这些高带宽功能的Speedster22i器件中,其片芯面积要大大小于一片可完成相同功能的等量其他FPGA厂商的器件,因此,可以实现功率和成本均减半。此外,Speedster22i器件中的硬核IP消除了这些高带宽功能的设计周期挑战,这也意味着整体的设计时间是在Altera或Xinlinx FPGA中构建同样功能的一半。

Achronix可以通过在其Speedster22i FPGA开发中使用来自于英特尔的硬核IP来降低其设计成本。掩膜费用是开发FPGA时的一种正常成本,相对于巨大而高利润的FPGA市场,掩膜是相对很小的一种成本。

问:业界通常认为,随着工艺进步,芯片的设计成本也将急剧上升,由32nm的5000-9000万美元至22nm时的1.2亿-5亿美元。这样一个32nm芯片从投资回报率角度需要售出3000-4000万块,而到20nm时需要6000万至10亿块,才能达到财务平衡点。而工艺尺寸达到22nm或20nm时,可能通用的成本下降理论已不再适用,导致产品会优先选择成熟的65nm、45nm或32nm工艺。对此Achronix有何看法?

Achronix:新工艺的开发费用会更高,但是,它也常常被高估。Achronix器件中的硬核IP给我们的目标应用带来显著的价值。我们潜在的商业机会远远大于22nm和未来工艺的盈亏平衡点。

问:“开发时间减半”,理由是否是:由于采用了硬IP?

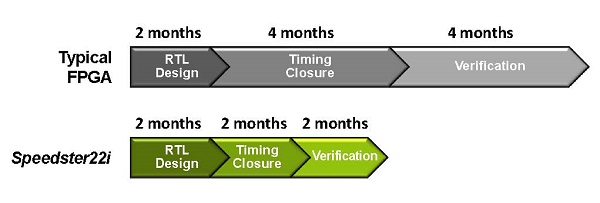

Achronix:是的,Speedster22i器件中的硬核IP消除了高带宽连接通信功能设计收敛时间的挑战。设计时间的节省范围包括RTL开发时间、验证时间、时序收敛和系统测试时间。与在Altera或Xilinx FPGA中构建相同功能所用时间相比,整体设计时间减为一半。

小结

只有85人的Achronix没被22nm烧钱的预言吓住,并打破了22nm设计的价格神话。技术创新使Achronix成为黑马。也提示我们不要被各种条条框框畏首畏尾。

参考文章:

[1]王莹.Achronix闯入,FPGA会发生地震吗?(2013-2-26).http://wangying1.spaces.eepw.com.cn/articles/article/item/94940

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。