SiC功率器件先进互连工艺研究

摘要:

针对SiC功率器件封装的高性能和高可靠性要求,文章研究了芯片双面银烧结技术与粗铜线超声键合技术的高可靠性先进互连工艺。通过系列质量评估与测试方法对比分析了不同烧结工艺对芯片双面银烧结层和芯片剪切强度的影响,分析了衬板表面材料对铜线键合强度的影响,最后对试制样品进行温度冲击测试,讨论了温度冲击对银烧结显微组织及其剪切强度的影响,以及对铜线键合强度的影响。试验结果表明:一次烧结工艺与分次烧结工艺的芯片剪切强度均达到了工业生产要求的标准值,但分次烧结工艺的银烧结效果在组织结构和芯片剪切强度上都要优于一次烧结工艺;温度冲击测试后烧结银显微组织的烧结颈增大,孔隙增大,并且2种烧结工艺的芯片剪切强度都明显增大。衬板材质对铜线超声键合强度有很大影响,在裸铜活性金属钎焊(ActiveMetalBraze,AMB)上的键合性能表现出更好的力学性能,温度冲击后裸铜AMB上的键合点力学性能会退化,但镀银AMB上的力学性能反而会增强;结合拉力测试后第二键合点的断裂模式,温度冲击使裸铜AMB上键合点的断裂模式从100%颈部断裂转向焊点脱落,而使镀银AMB上的焊点脱落逐渐减少。

0 引言

目前,功率开关器件发展迅速并被广泛运用,其设计与制造朝着高频开关速率、高功率密度、高结温等方向发展,尤其是SiC材料的出现,相对于传统的Si基材料,SiC半导体芯片有着高结温(最高有望超过600℃)、低导通电阻、高临界击穿场强、高开关频率等性能优势[1-2],但受限于器件封装技术,采用传统的Si基器件封装工艺制造出来的SiC功率开关器件,未能充分展现上述的SiC芯片性能优势。在常规封装的功率开关器件中,芯片底部的互连一般采用钎焊工艺,考虑到无铅化的要求,所选择的焊料熔点都低于250℃,如常用的SnAgCu系和SnSb系焊料等,因此不能充分发挥SiC芯片的高耐温性能。此外,焊料在界面处极易产生脆硬的金属间化合物,给产品的可靠性带来了新的挑战。目前,低温纳米银烧结技术是一种有效解决方案,银因其熔点高达961℃,将其作为连接材料能极大提高器件封装结构的温度耐受性,而纳米银的烧结温度却低于290℃,使用远低于熔点的烧结温度就能得到较为致密的组织结构,烧结后的银层耐热温度高,连接强度高,导热、导电性能良好[3-6]。

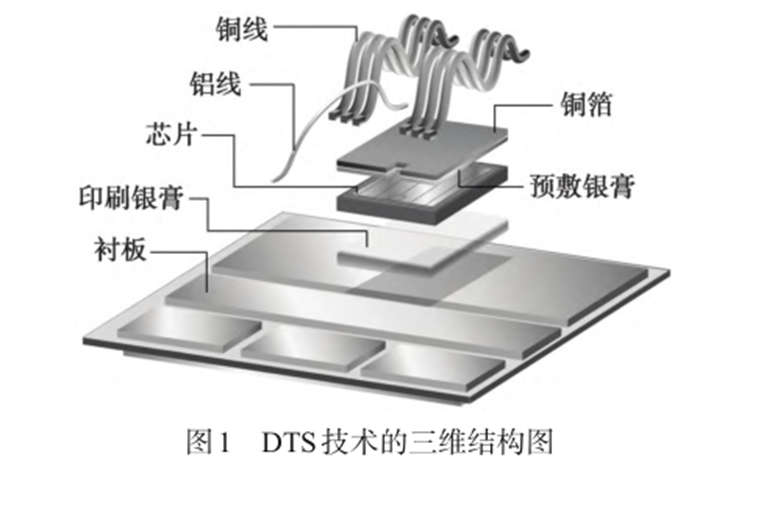

传统的Si基半导体芯片正面电极与外部互连采用的是铝线键合技术,由于铝线的再结晶温度低、电阻率高、屈服强度低等材料本身的局限性,这种连接方式并不能完全发挥SiC芯片的优势。相对于铝线而言,铜线材质具有更低的电阻率、更高的屈服强度、更强的导热性和机械稳定性等优点,其键合点的可靠性寿命与剪切强度都远高于铝线[7-9];然而铜线的硬度和加工硬化比铝线高,铜线键合时使用的超声压力与超声功率也比铝线高,这些问题都容易导致电极下方的芯片出现裂纹等损伤,因此不能直接在芯片正面使用粗铜线键合。本文采用的DTS(DieTopSystem)技术结合了芯片双面银烧结工艺与铜线键合工艺,此技术能够避免直接在芯片上进行铜线键合时造成的芯片损伤,相较于常规使用的芯片钎焊互连和铝线键合工艺,该技术能将功率器件的功率循环寿命提高数十倍。本文在此技术的工艺基础上,探索了芯片表面与底部的不同烧结工艺对烧结层的影响,以及衬板材质对铜线键合的影响。

1 试验方法与步骤

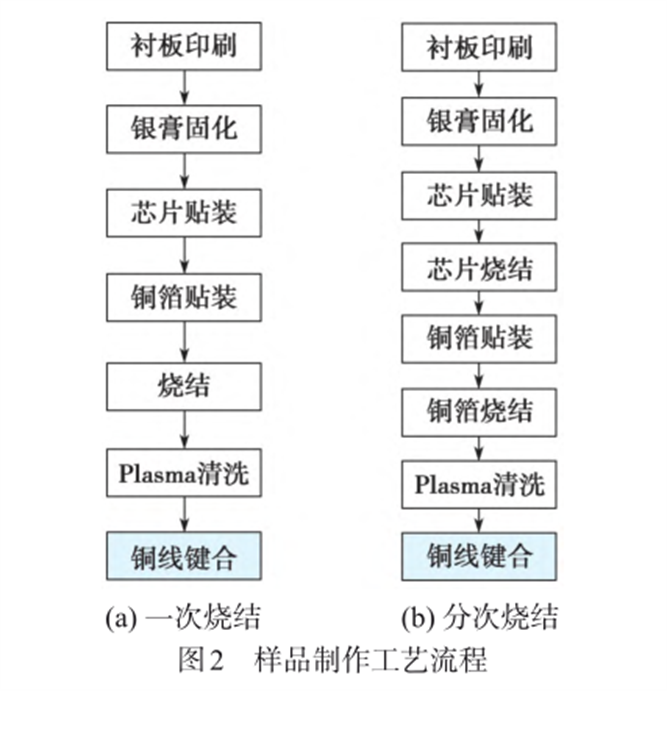

本文采用的基于DTS技术的封装形式如图1所示,先将芯片底部与衬板烧结连接,然后将芯片的正面电极区域覆盖一层敷银膏的铜箔(厚度约50~200μm)并烧结成型,最后在此铜箔上进行铜线键合。本试验采用的烧结工艺分别为一次烧结与分次烧结,其工艺流程如图2所示。选取了高可靠性的Si3N4活性金属钎焊(activemetalbraze,AMB)衬板,衬板表面材质分为裸铜与镀银2种,分别称为裸铜AMB与镀银AMB。本试验的银烧结工艺采用Alpha微纳米银膏,在相关烧结设备上进行银烧结;使用300μm线径的粗铜线,在超声楔形键合设备上进行铜线键合,研究裸铜AMB与镀银AMB衬板材质对铜线键合的影响。

铜线键合后将一部分样品放入炉中进行温度冲击试验(TemperatureShockTest,TST),试验的条件为-40℃(20min)/150℃(20min)。将温度冲击试验前后的样品采用超声扫描设备观察芯片双面烧结层的烧结情况,采用扫描电镜(ScanningElectronMicrosco‐py,SEM)观察分次烧结工艺后芯片底部的烧结层横截面的显微组织;采用推拉力设备进行芯片剪切强度测试,利用光学显微镜观察剪切断点位置的形貌,再对键合铜线进行拉力与剪切测试,利用光学显微镜观察拉断点形貌,最后分析各种条件下的芯片剪切强度与键合铜线测试数据。

2 试验结果与分析

2.1 银烧结效果分析

银烧结是一种基于原子扩散的固态物质运输过程,其驱动力是总表面能的降低,以及界面能的降低,银颗粒尺寸越小其表面能越高,烧结驱动力越大,还可以通过外部施加的压力来增强此驱动力[10]39-75。银烧结主要有3个阶段:初始阶段以表面原子扩散为特征,烧结颈是在颗粒之间相互以点或者面接触形成的,此阶段对致密化的贡献最大限制在2%~3%;中间阶段以致密化为特征,发生在形成独立孔隙之前,此阶段致密化达到93%;最后阶段是形成独立孔隙后的烧结,此阶段小孔隙逐渐消失,大孔隙逐渐变小,形成最终组织致密的烧结银[10-11]。

在不同烧结工艺条件下,在镀银AMB上银烧结的烧结层超声扫描结果如图3所示,在超声扫描图中烧结区域的颜色越深则表示孔隙越少,烧结层致密度越高。在分次烧结工艺条件下,芯片表面与底部的烧结层均有比较好的烧结效果,烧结层的均匀性好;但在一次烧结工艺条件下,芯片底部烧结区域呈现出明显的颜色差别,颜色深的位置对应于铜箔贴片位置,芯片上铜箔未覆盖的区域颜色较浅,烧结效果较差,此区域相对铜箔覆盖的区域所受的压力小,而银烧结的致密度与烧结压力有很大关系,适当的烧结压力对银烧结层的致密度与力学性能有很大影响,一方面能增强银膏与衬板之间的接触,加快银膏与衬板中的金属原子相互扩散;另一方面也有助于烧结层界面处银颗粒的重新排列,增强烧结界面处的银颗粒填充密度,减少烧结层组织的孔隙率[10,12]。

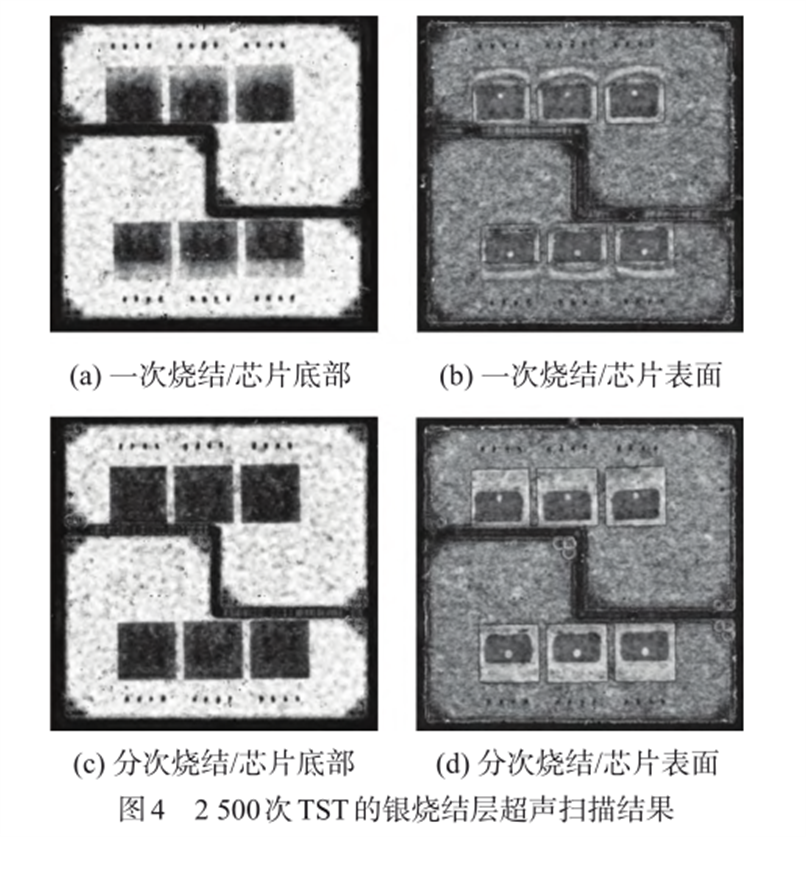

图4为在2种烧结工艺条件下,经过2500次温度冲击后的芯片底部和表面的烧结效果。由图4可知,芯片底部和表面的烧结未发生明显变化,未见明显的空洞或者裂纹;但芯片表面的烧结银面积缩小,均发生在芯片上的铜箔4个角的位置,这主要是由于温度冲击产生的应力导致铜箔4个角位置卷起,从而导致超声扫描结果显示4个角位置的烧结银面积缩小。

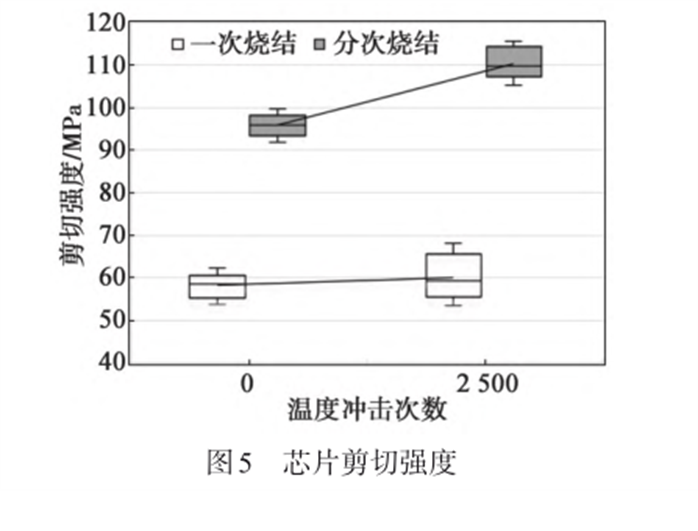

对不同烧结工艺的样品进行芯片剪切强度测试,每组条件测试12个芯片,其剪切强度测试结果如图5所示。由图5可知,烧结后(0次TST)一次烧结工艺与分次烧结工艺的芯片剪切强度均达到40MPa,剪切强度均达到了工业生产要求的标准值,但分次烧结工艺的剪切强度明显优于一次烧结工艺,此外2500次温度冲击后2种烧结工艺的芯片剪切强度都明显增大,以下结合芯片剪切断裂模式作进一步解释。

典型的剪切断裂一般发生在银烧结层(表示为“A”)或界面处(表示为“B”),也有可能是A与B的混合断裂模式,一般在银烧结层内部断裂是强接头的表现,而在界面处断裂相对来说是弱接头的表现[13]。如图6所示,一次烧结工艺与分次烧结工艺的断裂模式都是A与B的混合模式;观察一次烧结工艺的芯片剪切断面可发现,A断裂模式的所在位置正好是铜箔位置,也就是超声扫描显示颜色深的区域,如图6(a)和图6(b)所示,而B断裂模式所对应的位置则是超声扫描显示颜色相对浅的区域,如前所述铜箔覆盖的区域所承受的压力会大一些,其烧结效果更好,因此,此区域的断裂模式是从烧结层内部断裂,但烧结效果差的区域则从芯片与烧结层的界面处断裂;2500次TST后A断裂模式的面积增大而B断裂模式的面积减小,这也印证了TST后剪切强度增大的现象。分次烧结工艺的剪切强度明显优于一次烧结工艺,观察芯片的剪切断面,对比一次烧结工艺,分次烧结工艺的A断裂模式面积明显变大,如图6(c)所示,覆盖了芯片剪切断面的大部分区域,说明此时是强接头的表现;此外,分次烧结工艺的样品在2500次TST后A断裂模式的面积也同样增大,如图6(d)所示。

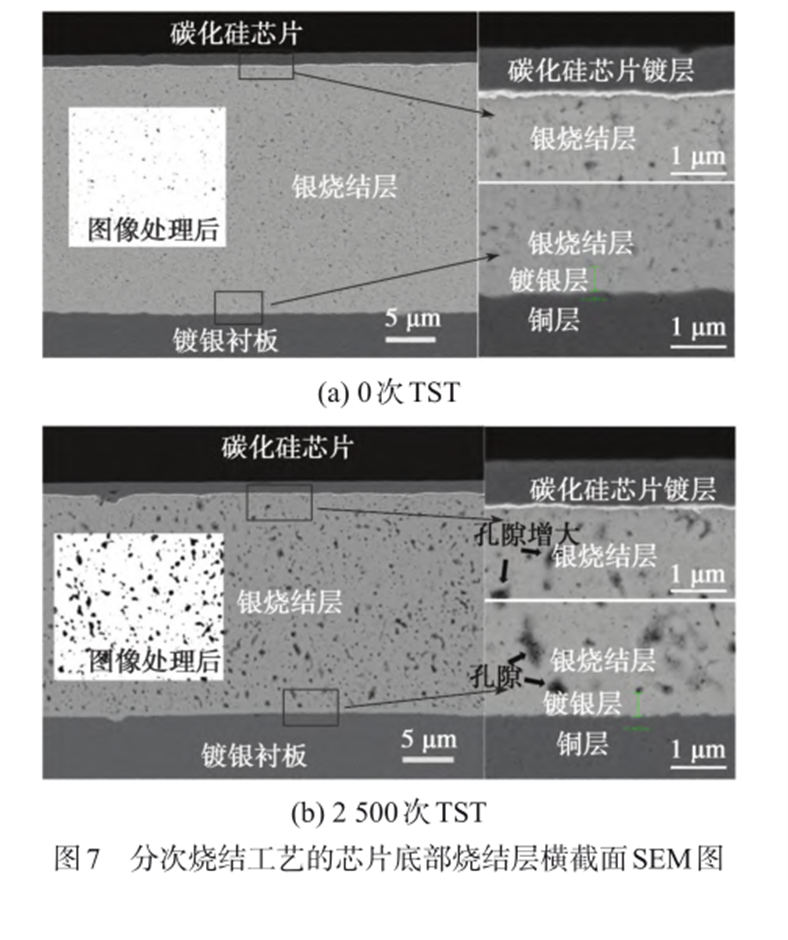

评价银烧结显微组织的几个关键参数包含孔隙大小、孔隙率、孔隙的形状和分布、晶粒尺寸。孔隙是银烧结过程中银颗粒之间的空隙,其形成取决于银颗粒之间的烧结颈,以及随后的烧结颈生长情况,烧结颈的形成依赖于烧结温度,适当提高烧结温度和延长烧结时间有利于烧结颈的生长;适当提高烧结压强和烧结温度可以减小烧结银中的大孔隙,降低孔隙率,提高烧结银的致密度[14]。孔隙会引起热流和电流集中,增加烧结银在实际应用中失效的可能性;随着孔隙率的增加,纳米银的导热系数会降低,电阻率会增大[15]。如图7所示,对分次烧结工艺的芯片底部烧结层横截面使用扫描电镜观察其显微组织,在此试验烧结条件下烧结后(0次TST)得到的银烧结层是孔隙分布均匀且组织致密的多孔性结构,通过软件对局部区域进行灰度处理后,计算出孔隙率为1.98%;2500次TST后孔隙增大,晶粒尺寸也进一步长大,孔隙率为8.31%;此外,在烧结层与衬板镀银层之间的界面观察到明显的孔隙增大,这是由于在温度冲击的作用下镀银层下面的铜原子会扩散到衬板表面,继而发生氧化,铜氧化物与铜或银的热膨胀系数不匹配,从而导致了较大的热应力,引起孔隙进一步增大。

2.2 铜线超声键合结果与分析

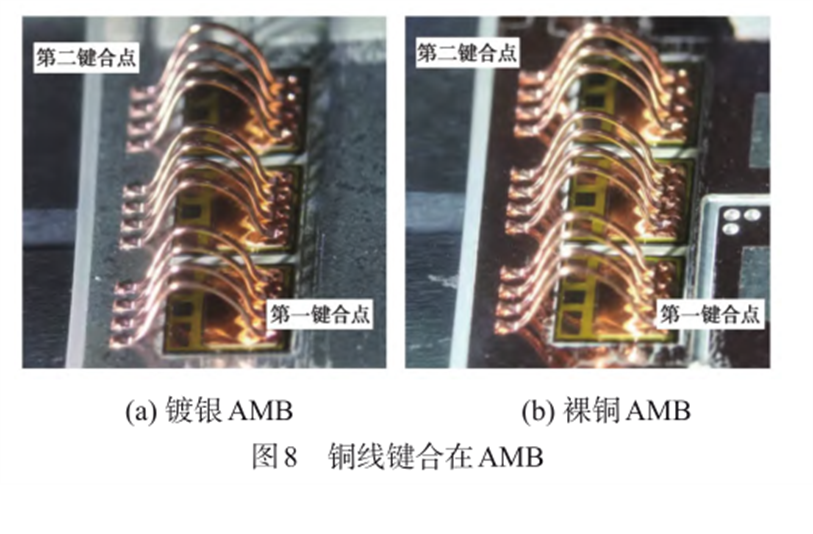

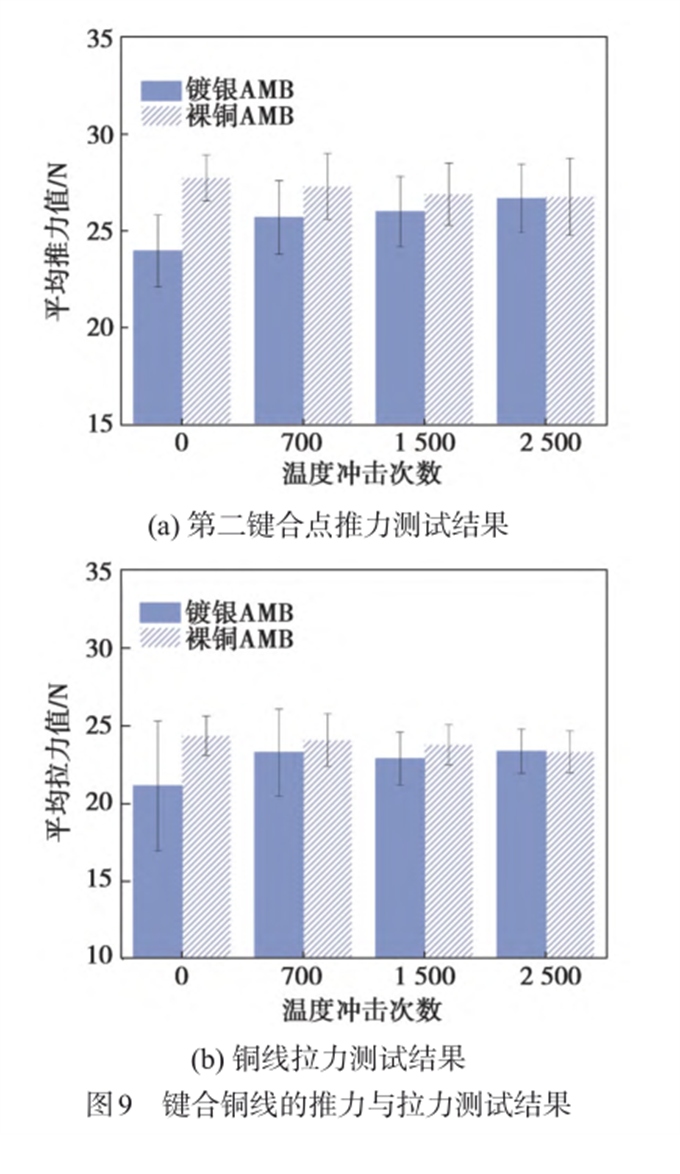

在超声键合过程中,通过劈刀施加压力使引线与焊区变形,结合超声波振动促进引线与焊区之间的相互摩擦,破坏引线与焊区表面的氧化膜,促进键合界面处的相互扩散,达到引线与焊区的固相键合。超声键合的关键参数是超声波振动功率、压力和键合时间。压力可造成引线的弹性变形,与压力相比,超声波振动更能促进引线变形,影响引线的塑性变形。铜的强度和加工硬化性比铝高,因此铜线超声键合所需的超声功率和压力也相应高一些。使用相同的工艺参数将铜线键合在镀银AMB与裸铜AMB上,如图8所示,在不同温度冲击条件下随机选取第二键合点的24个焊点进行剪切试验,同时在不同温度冲击条件下随机选取24根键合铜线进行拉力试验。图9为2种材质的衬板铜线键合后对第二键合点进行剪切试验的平均推力值和拉力试验的平均拉力值。

由图9(a)可知,键合后(0次TST),在裸铜AMB上键合的第二焊点平均推力值要比在镀银AMB键合的平均推力值高,这可以用Cu/Cu同质结合比Cu/Ag异质结合的界面结合强度要高来解释[16];然而随着温度冲击的次数逐渐增加到2500次,在裸铜AMB上键合的第二焊点推力平均值逐渐减小,但在镀银AMB上键合的第二焊点推力平均值却逐渐增大。由图9(b)可知,对键合铜线进行拉力测试,其平均拉力值的变化也有相同的趋势,随着温度冲击的次数逐渐增加到2500次,裸铜AMB上的键合铜线拉力值逐渐减小,而镀银AMB上的键合铜线拉力值却逐渐增大,这需要结合拉力测试后第二焊点的失效模式做进一步解释。

铜线拉力测试后第二焊点表现的失效模式主要有2种:颈部断裂和焊点脱落。相对而言,颈部断裂模式下的强度要高于焊点脱落模式。图10为在裸铜AMB和镀银AMB上进行铜线键合后第二焊点失效模式图片和统计数据。由图10(a)可知,烧结后(0次TST)的失效模式是颈部断裂,这是由于在键合过程中焊点颈部的形变最大,导致这部分出现应变硬化,延展性较差,容易发生断裂;在经历2500次温度冲击后出现焊点脱落,失效占比约为20.83%,说明此时键合点与裸铜AMB界面之间的相互连接趋于弱化,这是由于温度冲击产生的热应力导致界面附近逐渐产生微裂纹并且长大,进而表现出键合铜线的推拉力平均值逐渐下降的

现象。由图10(b)可知,烧结后(0次TST)的失效模式是颈部断裂与焊点脱落,焊点脱落仅略低于颈部断裂,失效占比约为45.83%,这表明此时键合铜线与镀银衬板的键合点界面之间结合得并不理想;然而在经历2500次温度冲击后,键合点的焊点脱落失效却减少了,失效占比约为16.67%,表现为键合铜线的推拉力平均值逐渐上升,这可能是由于键合界面处的铜原子与银原子在温度的作用下相互扩散,导致界面金属之间出现化合物,使得键合强度增加,但持续增加温度冲击次数对其键合点力学性能的影响还有待进一步研究。

3 结论

本文研究了基于DTS技术的不同烧结工艺对烧结层的影响和AMB衬板材质对铜线键合的影响,结论如下:

①一次烧结工艺与分次烧结工艺的芯片剪切强度均达到了工业生产要求的标准值,但分次烧结工艺的银烧结效果在组织结构和力学性能上都要优于一次烧结工艺,而温度冲击使得2种烧结工艺的芯片剪切强度都明显增大,结合芯片剪切断面观察发现其断裂路径从界面转向烧结层内部。

②衬板材质对铜线超声键合有很大影响,裸铜AMB由于铜/铜同质结合键合点表现出更好的力学性能,当温度冲击次数增加到2500次时裸铜AMB上的键合点力学性能会退化,但镀银AMB上的力学性能反而会加强,这可能与生成界面金属间化合物有关,而持续增加温度冲击次数对其键合点力学性能的影响还有待进一步研究。

综合来说,相对于使用芯片钎焊互连和铝线键合工艺,芯片双面银烧结技术和铜线键合技术表现出更为优异的力学性能和高可靠性,适合应用于碳化硅功率模块的封装工艺。但是目前关于银烧结技术和粗铜线超声键合技术在高温可靠性方面的研究还比较少,仍需进行深入的探讨与研究。

来源:半导体封装工程师之家

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。